## Projecto e Controlo em Lógica Digital

#### www.lip.pt/~pedjor/PCLD2014

- Combinational logic

- Modules

- Sequential Logic

- Tools

#### **Refs:**

Cyclone II device Handbook, Altera corp.

Quartus II Handbook, Altera corp.

DE2 documentation

Verilog HDL, S. Palnitkar, Prentice Hall

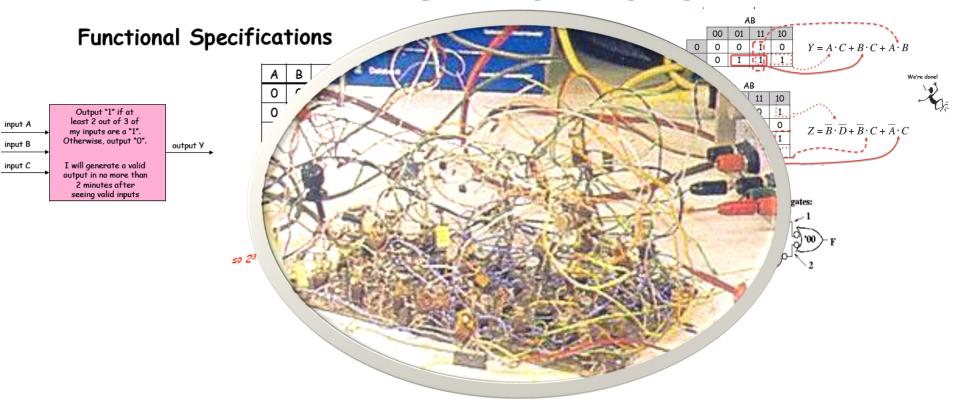

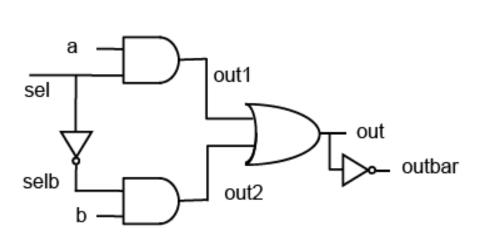

## 74LS.... vs FPGAs

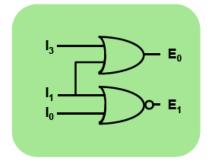

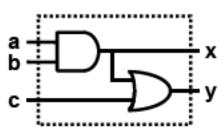

### Gate Level Description

Verilog has built-in basic logic gates: And, nand, or, nor, xor, xnor, not, buf

WIRE: represents connections between elements.

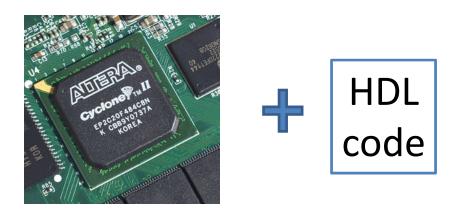

#### Building a multiplexer using gates

#### The HDL

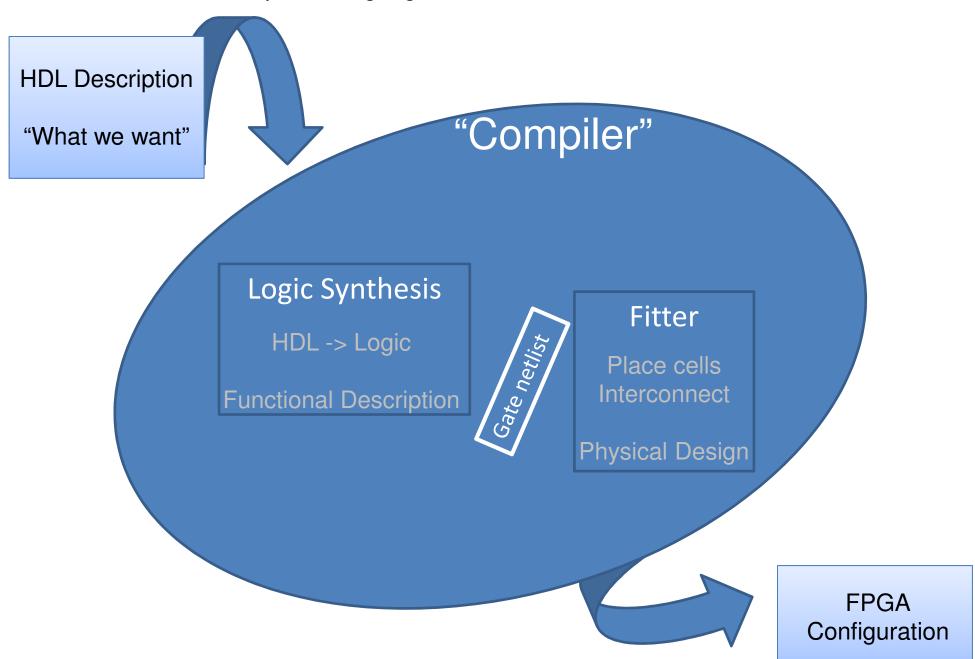

#### HDL = Hardware Description Language

4

## Verilog data values

| Value  | Meaning                    |  |

|--------|----------------------------|--|

| 0      | Logic zero, "Low"          |  |

| 1      | Logic one, "High"          |  |

| Z or ? | High Impedance (tri-state) |  |

| X      | Unknow (simulation)        |  |

#### Numeric constants

Full format: <Width>'<Radix>value

Width: number

Radix: d=decimal, h=hex, o=ocatl, b=binary

| Value     | Meaning                                  |

|-----------|------------------------------------------|

| 123       | Default: decimal radix                   |

| 'd123     | 'd=decimal radix                         |

| ʻh7B      | 'h=hexadecimal radix                     |

| ʻo173     | 'o=ocatl radix                           |

| 'b111_101 | 'b=binary radix                          |

| 16'b11111 | A binary with 16 bits                    |

| 16'd5     | A 16 bit decimal = 'b0000_0000_0000_0101 |

## **Boolean operators**

- Bitwise operators perform bit-oriented operations on vectors

- ~(4'b0101) = {~0,~1,~0,~1} = 4'b1010

- 4'b0101 & 4'b0011 = {0&0, 1&0, 0&1, 1&1} = 4'b0001

- · Reduction operators act on each bit of a single input vector

- &(4'b0101) = 0 & 1 & 0 & 1 = 1'b0

- Logical operators return one-bit (true/false) results

- !(4'b0101) = 1'b0

#### **Bitwise**

| ~a               | NOT  |

|------------------|------|

| a&b              | AND  |

| a b              | OR   |

| a^b              | XOR  |

| a ~^ b<br>a ^~ b | XNOR |

#### Reduction

| &a         | AND  |

|------------|------|

| ~&a        | NAND |

| a          | OR   |

| ~ a        | NOR  |

| ^a         | XOR  |

| ~^a<br>^~a | XNOR |

Note distinction between ~a and !a when operating on multi-bit values

Logical

| !a                 | NOT                                                                         |

|--------------------|-----------------------------------------------------------------------------|

| a && b             | AND                                                                         |

| a    b             | OR                                                                          |

| a == b<br>a != b   | [in]equality<br>returns x when x<br>or z in bits. Else<br>returns 0 or 1    |

| a === b<br>a !== b | case<br>[in]equality<br>returns 0 or 1<br>based on bit by<br>bit comparison |

## Other operators

#### Conditional

#### Relational

| a>b    | greater than          |  |

|--------|-----------------------|--|

| a >= b | greater than or equal |  |

| a < b  | Less than             |  |

| a <= b | Less than or equal    |  |

#### Arithmetic

| -a      | negate                 |

|---------|------------------------|

| a+b     | add                    |

| a - b   | subtract               |

| a*b     | multiply               |

| a/b     | divide                 |

| a%b     | modulus                |

| a ** b  | exponentiate           |

| a << b  | logical left shift     |

| a >> b  | logical right shift    |

| a <<< b | arithmetic left shift  |

| a >>> b | arithmetic right shift |

## How many bits?

| Wire ab;        | A 1 bit wire called <u>ab</u>                    |

|-----------------|--------------------------------------------------|

| Wire ab,cd;     | Two 1 bit wires called <u>ab</u> and <u>cd</u>   |

| wire [31:0] ef; | A 32 bits wire bus called <u>ef</u> ;            |

| {ab,cd}         | Concatenation of <u>ab</u> and <u>cd</u> ;       |

| ef[15]          | Bit #15 (the sixteenth) of <u>ef</u>             |

| ef[7:0]         | First 8 bits of <u>ef</u> (the ones to the right |

#### What does this means?

```

wire [31:0] kk;

Wire [7:0] a,b,c,d;

Assign kk={d,c,b,a}

```

```

Note:

```

wire [7:0]a; wire [0:7]b;

The two forms can be used. Prone to error if mixed.

Standard convention: [MSB:LSB] w/ MSB>LSB & LSB=0

[WIDTH-1:0]

## The REG keyword

reg = register is intended as a variable type

#### LeftHandSide inside always blocks must be reg!

For historical reasons... reg is not always a clocked register (althought it would make more sense)

```

reg can be used directly in the port declaration:

output reg [15:0] result

or in the declaration of a net:

reg a;

reg[31:0] b;

```

Do not use reg with assigns: reg out; assign out=0;

## Continuous Assignments

(aka dataflow)

```

The assign construction assign LHS = RHS; can use operators...

```

```

wire a,b,c,d,e,f,g;

assign a=b;

assign c=!d;

assign e=f+g;

```

## Sequential behaviours

(aka procedural)

```

The "always @" construction always @ (sensitivity list) begin

LHS=RHS; end can use operators, if, case, ...

```

```

wire b,d,f,g;

reg a,c,e;

always @ (b,d,f,g)

begin

a=b;

c=!d;

e=f+g;

end

can be:

always @ (*)

```

## ASSIGN

# // 2-to-1 multiplexer with dual-polarity outputs module mux2(input a,b,sel, output z,zbar); // again order doesn't matter (concurrent execution!) // syntax is "assign LHS = RHS" where LHS is a wire/bus // and RHS is an expression assign z = sel ? b : a; assign zbar = ~z; endmodule

## ALWAYS @ IF...THEN...ELSE

```

// 4-to-1 multiplexer

module mux4(input a,b,c,d, input [1:0] sel, output reg z,zbar);

always @(*) begin

if (sel == 2'b00) z = a;

else if (sel == 2'b01) z = b;

else if (sel == 2'b10) z = c;

else if (sel == 2'b11) z = d;

else z = 1'bx; // when sel is X or Z

// statement order matters inside always blocks

// so the following assignment happens *after* the

// if statement has been evaluated

zbar = ~z;

end

endmodule

```

```

ALWAYS @

```

```

// 4-to-1 multiplexer

module mux4(input a,b,c,d, input [1:0] sel, output reg z,zbar);

always @(*) begin

case (sel)

2'b00: z = a;

2'b01: z = b;

2'b10: z = c;

2'b11: z = d;

default: z = 1'bx; // in case sel is X or Z

endcase

zbar = ~z;

end

endmodule

```

## Mix Assignments

- Procedural and continuous assignments can (and often do) co-exist within a module

- Procedural assignments update the value of reg. The value will remain unchanged till another procedural assignment updates the variable.

This is the main difference with continuous assignments in which the right hand expression is constantly placed on the left-side

```

module mux 2 to 1(a, b, out,

outbar, sel);

input a, b, sel;

output out, outbar;

reg out;

always @ (a or b or sel)

begin

procedural

if (sel) out = a;

else out = b;

description

end

continuous

assign outbar = ~out;

description

endmodule

```

#### n-bit signals

- Multi-bit signals and buses are easy in Verilog.

- 2-to-1 multiplexer with 8-bit operands:

{m,n} Concatenate m to n, creating larger vector

```

// if the MSB of a is high, this module

// concatenates 1111 to the vector. With signed

// binary numbers, this is called sign extension.

module sign_extend(a, out);

input [3:0] a;

output [7:0] out;

assign out = a[3] ? {4'b1111,a} : {4'b0000,a};

endmodule

```

### **Integer Arithmetic**

Verilog's built-in arithmetic makes a 32-bit adder easy:

```

module add32(a, b, sum);

input[31:0] a,b;

output[31:0] sum;

assign sum = a + b;

endmodule

```

#### A 32-bit adder with carry-in and carry-out:

```

module add32_carry(a, b, cin, sum, cout);

input[31:0] a,b;

input cin;

output[31:0] sum;

output cout;

assign {cout, sum} = a + b + cin;

endmodule

```

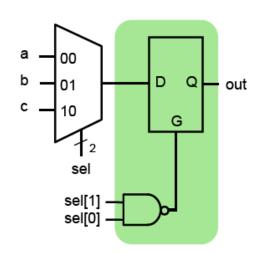

## Danger

#### Goal:

#### **Proposed Verilog Code:**

If out is not assigned during any pass through the always block, then the previous value must be retained

**LATCH**

#### Synthesized Result:

- Latch memory "latches" old data when G=0 (we will discuss latches later)

- In practice, we almost never intend this

#### Solution:

Precede all conditionals with a default assignment for all signals assigned within them...

```

always @(a or b or c or sel)

begin

out = 1'bx;

case (sel)

2'b00: out = a;

2'b01: out = b;

2'b10: out = c;

endcase

end

endmodule

```

```

always @(a or b or c or sel)

begin

case (sel)

2'b00: out = a;

2'b01: out = b;

2'b10: out = c;

default: out = 1'bx;

endcase

end

endmodule

```

- ...or, fully specify all branches of conditionals <u>and</u> assign all signals from all branches

- □ For each if, include else

- ☐ For each case, include default

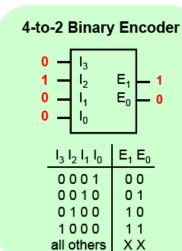

#### Goal:

#### **Proposed Verilog Code:**

```

module binary_encoder(i, e);

input [3:0] i;

output [1:0] e;

reg [1:0] e;

always @(i)

begin

if (i[0]) e = 2'b00;

else if (i[1]) e = 2'b01;

else if (i[2]) e = 2'b10;

else if (i[3]) e = 2'b11;

else e = 2'bxx;

end

endmodule

```

What is the resulting circuit?

Code: if i[0] is 1, the result is 00 regardless of the other inputs. i[0] takes the highest priority.

```

if (i[0]) e = 2'b00;

else if (i[1]) e = 2'b01;

else if (i[2]) e = 2'b10;

else if (i[3]) e = 2'b11;

else e = 2'bxx;

end

```

If-else and case statements are interpreted very literally!

Beware of unintended priority logic

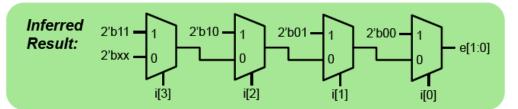

#### Solution:

- Make sure that if-else and case statements are parallel

- ☐ If mutually exclusive conditions are chosen for each branch...

- ...then synthesis tool can generate a simpler circuit that evaluates the branches in parallel

#### Parallel Code:

```

module binary_encoder(i, e);

input [3:0] i;

output [1:0] e;

reg [1:0] e;

always @(i)

begin

if (i == 4'b0001) e = 2'b00;

else if (i == 4'b0010) e = 2'b11;

else if (i == 4'b1000) e = 2'b11;

else e = 2'bxx;

end

endmodule

```

#### Minimized Result:

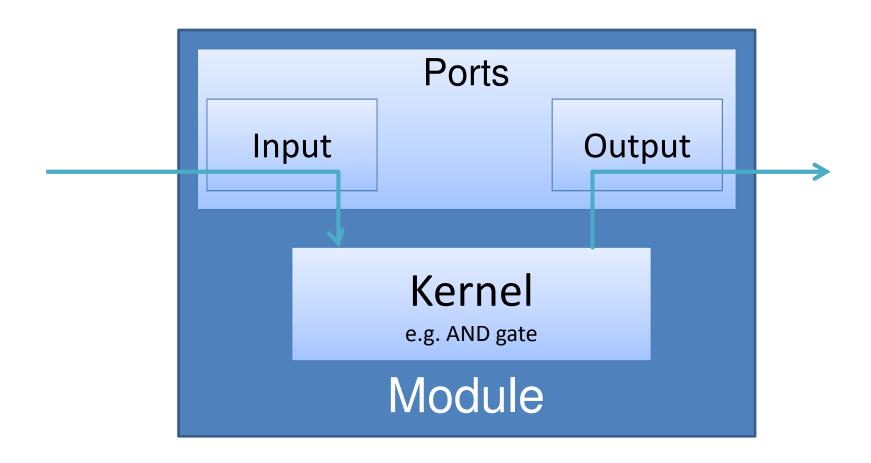

## Modules, again, and again and again...

## Structuring... Modules

Modules are the building blocks in Verilog!

There is at least one module: The top one that has the name of the project!

Ports in the top level module link directly to the pins

## Modules with different juice...

#### module mux(input a,b,sel, output q, qbar);

```

wire selbar, q1, q2; not n1(selbar, sel); and a1(q1, a, selbar); and a2(z2, b, sel); or o1(q, q1, q2); not n2(qbar, q)  \begin{array}{l} assign \ q = sel? \ a : \ b; \\ assign \ qbar = \sim \ q; \\ assign \ qbar

```

#### endmodule

We just need to know the shell, the interface, and its function!

### Call the port by its name!

#### module mux(i0,i1,i2,sel,out);

```

Option 1: Know the order and write all ports...

mux my mux (add out, sub out, mul out, f[1:0], res);

Option 2: Know their names...

syntax: module_type module_name (.port_name(net_name), .port2_name(net2_name));

mux my_mux (.sel(f[1:0]),

mux my_mux (.i0(add_out),

.out(res),

.i1(sub_out),

OR

.i2(mul_out),

.iO(add_out),

.i1(sub_out),

.sel(f[1:0]),

.i2(mul_out),

.out(res));

port

net

name

mux my_mux (.sel(2'b00),

.out(res),

.i0(add_out),

even

20

```

#### Parametrized modules

could be useful if we could build "generic" modules for instance a mux for data buses that can be 1 bit to 32bit if we have a parameter that seems easy

#### THE #(PARAMETER ....)

#### Using a parametrized module

```

wire a,b,c,z;

mux #(.W(1)) m1(.sel(a),.i0(b),.i1(c),.out(z));

wire aa;

wire [15:0] bb,cc,zz;

mux #(.W(16)) m1(.sel(aa),.i0(bb),.i1(cc),.out(zz));

```

#### and of course... be creative...

You can instantiante lots of modules that feeds one another... Each instance is like a "new chip" of that type Each instance must have different names

How many instances can drive a net??

Sometimes drawing in a paper is useful...

just draw boxes, don't need to be an artist...

```

// 4-to-1 multiplexer

module mux4(input d0,d1,d2,d3, input [1:0] sel, output z);

wire z1,z2;

// instances must have unique names within current module.

// connections are made using .portname(expression) syntax.

// once again order doesn't matter...

mux2 m1(.sel(sel[0]),.a(d0),.b(d1),.z(z1)); // not using zbar

mux2 m2(.sel(sel[0]),.a(d2),.b(d3),.z(z2));

mux2 m3(.sel(sel[1]),.a(z1),.b(z2),.z(z));

// could also write "mux2 m3(z1,z2,sel[1],z,)" NOT A GOOD IDEA!

endmodule

```

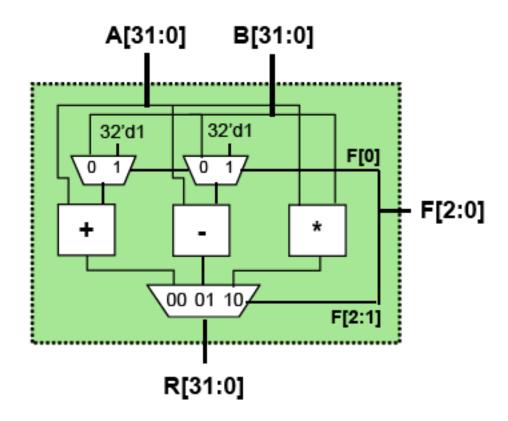

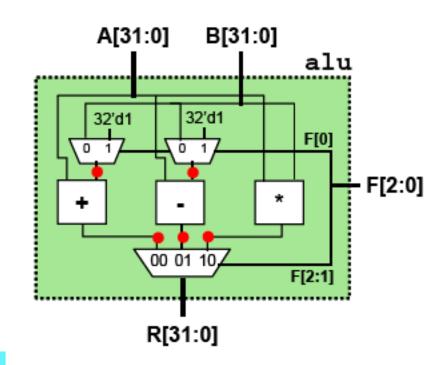

## Build an ALU

## Connecting modules to build complex machines

#### Example: A 32-bit ALU

#### **Function Table**

| F2 F1 F0 |   | F0 | Function |

|----------|---|----|----------|

| 0        | 0 | 0  | A + B    |

| 0        | 0 | 1  | A + 1    |

| 0        | 1 | 0  | A-B      |

| 0        | 1 | 1  | A - 1    |

| 1        | 0 | X  | A * B    |

|          |   |    | I        |

#### Modules

#### 2-to-1 MUX

```

module mux32two(10,11,sel,out);

input [31:0] 10,11;

input sel;

output [31:0] out;

assign out = sel ? 11 : 10;

endmodule

```

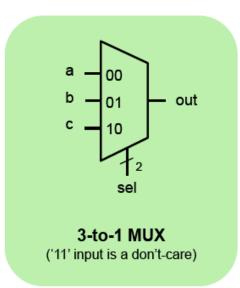

#### 3-to-1 MUX

```

module mux32three(10,11,12,sel,out);

input [31:0] 10,11,12;

input [1:0] sel;

output [31:0] out;

reg [31:0] out;

always @ (10 or 11 or 12 or sel)

begin

case (sel)

2'b00: out = 10;

2'b01: out = 11;

2'b10: out = 12;

default: out = 32'bx;

endcase

end

endmodule

```

#### 32-bit Adder

```

module add32(10,11,sum);

input [31:0] 10,11;

output [31:0] sum;

assign sum = 10 + 11;

```

endmodule

#### 32-bit Subtracter

```

module sub32(10,11,d1ff);

input [31:0] 10,11;

output [31:0] diff;

assign diff = 10 - 11;

endmodule

```

#### 16-bit Multiplier

```

module mul16(10,11,prod);

input [15:0] 10,11;

output [31:0] prod;

// this is a magnitude multiplier

// signed arithmetic later

assign prod = 10 * 11;

endmodule

```

### Top-Level: connect the modules

#### Given submodules:

```

module mux32two(10,11,sel,out);

module mux32three(10,11,12,sel,out);

module add32(10,11,sum);

module sub32(10,11,diff);

module mul16(10,11,prod);

```

#### Declaration of the ALU Module:

names

```

module alu(a, b, f, r);

input [31:0] a, b;

input [2:0] f;

output [31:0] r;

```

```

wire [31:0] addmux out, submux out;

wire [31:0] add out, sub out, mul out;

```

instance

names

```

mux32two

adder mux(b, 32'd1, f[0], addmux out);

sub mux(b, 32'd1, f[0], submux out);

mux32two

add32

our adder (a, addmux out, add out);

our subtracter (a, submux out, sub out);

sub32

our multiplier (a[15:0], b[15:0], mul out);

mul16

mux32three output mux(add out, sub out, mul out, f[2:1], r);

endmodule

module

(unique)

```

corresponding wires/regs in module alu

intermediate output nodes

## Until here: Combinational logic

## Sequential Logic

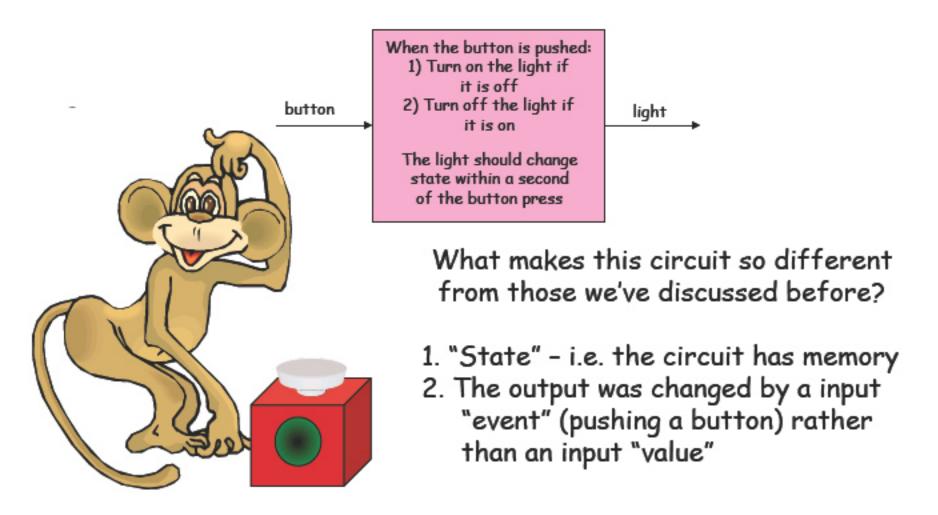

## Something We Can't Build (Yet)

What if you were given the following design specification:

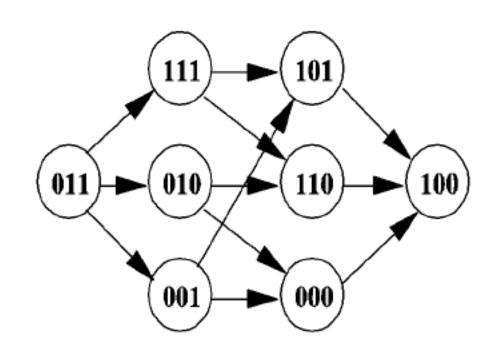

## Digital State

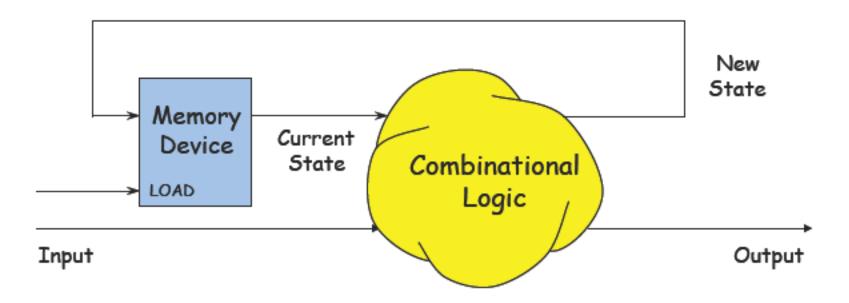

One model of what we'd like to build

Plan: Build a Sequential Circuit with stored digital STATE -

- Memory stores CURRENT state, produced at output

- Combinational Logic computes

- NEXT state (from input, current state)

- OUTPUT bit (from input, current state)

- State changes on LOAD control input

when Output depends on input and current state, circuit is called a Mealy machine. If Output depends <u>only</u> on the current state, circuit is called a Moore machine.

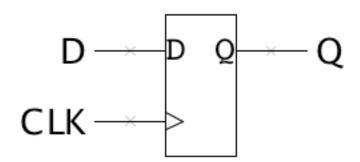

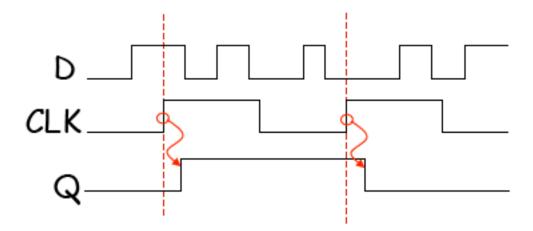

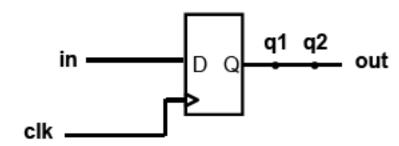

## Our next building block: the D register

The edge-triggered D register: on the rising edge of CLK, the value of D is saved in the register and then shortly afterwards appears on Q.

## The Sequential always Block

Edge-triggered circuits are described using a sequential always block

#### Combinational

#### <u>Sequential</u>

```

module seq(input a, b, sel, clk,

module comb(input a, b, sel,

output reg out);

output reg out);

always @(*) begin

always @(posedge clk) begin

if (sel) out = a;

if (sel) out <= a;

else out = b;

else out <= b;

end

end

endmodule

endmodule

а

a

out

out

b

sel

sel

clk

```

## Importance of the Sensitivity List

- The use of posedge and negedge makes an always block sequential (edge-triggered)

- Unlike a combinational always block, the sensitivity list does determine behavior for synthesis!

D-Register with synchronous clear

D-Register with asynchronous clear

```

module dff_sync_clear(

module dff_sync_clear(

input d, clearb, clock,

input d, clearb, clock,

output reg q

output reg q

):

);

always @(negedge clearb or posedge clock)

always @(posedge clock)

begin

begin

if (!clearb) q <= 1'b0;

if (!clearb) q \leftarrow 1'b0;

else q \ll d;

else q \ll d:

end

end

endmodule

endmodule

```

always block entered only at each positive clock edge

always block entered immediately when (active-low) clearb is asserted

Note: The following is incorrect syntax: always @(clear or negedge clock)

If one signal in the sensitivity list uses posedge/negedge, then all signals must.

Assign any signal or variable from <u>only one</u> always block. Be wary

of race conditions: always blocks with same trigger execute

concurrently...

## Blocking vs. Nonblocking Assignments

- Verilog supports two types of assignments within always blocks, with subtly different behaviors.

- Blocking assignment (=): evaluation and assignment are immediate

Nonblocking assignment (<=): all assignments deferred to end of simulation time step after <u>all</u> right-hand sides have been evaluated (even those in other active <u>always</u> blocks)

Sometimes, as above, both produce the same result. Sometimes, not!

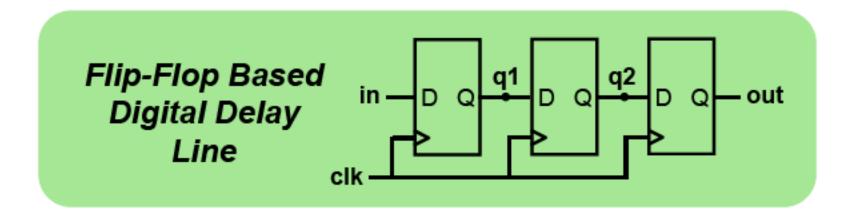

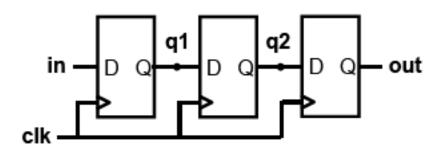

## Assignment styles for sequential logic

Will nonblocking and blocking assignments both produce the desired result?

```

module nonblocking(in, clk, out);

module blocking(in, clk, out);

input in, clk;

input in, clk;

output out;

output out;

reg q1, q2, out;

reg q1, q2, out;

always @ (posedge clk)

always @ (posedge clk)

begin

begin

q1 <= in;

q1 = in;

q2 <= q1;

q2 = q1;

out <= q2;

out = q2;

end

end

endmodule

endmodule

```

## Use nonblocking for sequential logic

```

always @ (posedge clk)

begin

q1 <= in;

q2 <= q1;

out <= q2;

end</pre>

```

"At each rising clock edge, q1, q2, and out simultaneously receive the old values of in, q1, and q2."

```

always @ (posedge clk)

begin

q1 = in;

q2 = q1;

out = q2;

end

"At each rising clock edge, q1

= in.

After that, q2 = q1 = in.

After that, out = q2 = q1 = in.

Therefore out = in."

```

- Blocking assignments do not reflect the intrinsic behavior of multi-stage sequential logic

- Guideline: use nonblocking assignments for sequential always blocks

# Use blocking for combinational logic

| Blocking Behavior                    | abc x y |

|--------------------------------------|---------|

| (Given) Initial Condition            | 11011   |

| a changes;<br>always block triggered | 01011   |

| x = a & b;                           | 01001   |

| y = x   c;                           | 01000   |

```

module blocking(a,b,c,x,y);

input a,b,c;

output x,y;

reg x,y;

always @ (a or b or c)

begin

x = a & b;

y = x | c;

end

endmodule

```

| No | nblocking Behavior                   | abcxy | Deferred   |

|----|--------------------------------------|-------|------------|

|    | (Given) Initial Condition            | 11011 |            |

|    | a changes;<br>always block triggered | 01011 |            |

|    | x <= a & b;                          | 01011 | x<=0       |

|    | y <= x   c;                          | 01011 | x<=0, y<=1 |

|    | Assignment completion                | 01001 |            |

|    |                                      |       |            |

```

module nonblocking(a,b,c,x,y);

input a,b,c;

output x,y;

reg x,y;

always @ (a or b or c)

begin

x <= a & b;

y <= x | c;

end

endmodule</pre>

```

- Nonblocking and blocking assignments will synthesize correctly. Will both styles simulate correctly?

- Nonblocking assignments do not reflect the intrinsic behavior of multi-stage combinational logic

- While nonblocking assignments can be hacked to simulate correctly (expand the sensitivity list), it's not elegant

- Guideline: use blocking assignments for combinational always blocks

# = vs <= inside always</pre>

```

always @(posedge clk) begin

a = b; // blocking assignment

b = a; // execute sequentially

end

always @(posedge clk) begin

a <= b; // non-blocking assignment

b <= a; // eval all RHSs first

end</pre>

```

Rule: <u>always</u> change state using <= (e.g., inside a lways @(posedge clk)...)

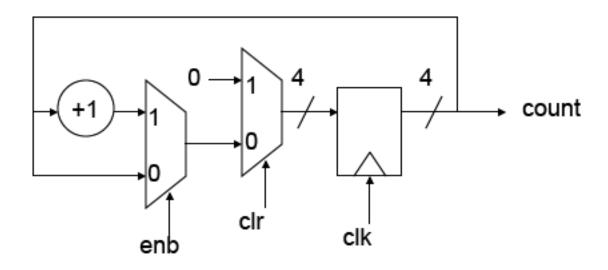

## Example: A simple counter

## Counter 32 bits in the leds...

## PWM – Pulse Width Modulation

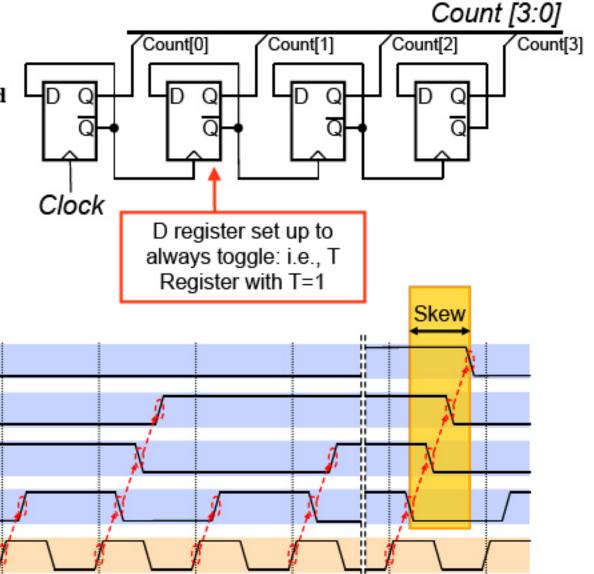

# The Asynchronous counter

### A simple counter architecture

- uses only registers

(e.g., 74HC393 uses T-register and negative edge-clocking)

- Toggle rate fastest for the LSB

...but ripple architecture leads to large skew between outputs

Count [3]

Count [2]

Count [1]

Count [0]

Clock

# The ripple counter in verilog

#### Single D Register with Asynchronous Clear:

```

module dreg async reset (clk, clear, d, q, qbar);

Count [3:0]

input d, clk, clear;

Count[0]

Count[1]

Count[2]

Count[3]

output q, qbar;

reg q;

always @ (posedge clk or negedge clear)

begin

Countbar[3]

if (!clear)

q <= 1'b0;

else q <= d;

Countbar[0]

Countbar[1]

Countbar[2]

end

assign qbar = ~q;

endmodule

```

#### Structural Description of Four-bit Ripple Counter:

# Logic for a synchronous counter

- Count (C) will retained by a D Register

- Next value of counter (N) computed by combinational logic

CLK-

- Any time multiple bits change, the counter output needs time to settle.

- Even though all flip-flops share the same clock, individual bits will change at different times.

- □ Clock skew, propagation time variations

- Can cause glitches in combinational logic driven by the counter

- The RCO can also have a glitch.

Care is required of the Ripple Carry Output: It can have glitches: Any of these transition paths are possible!

#

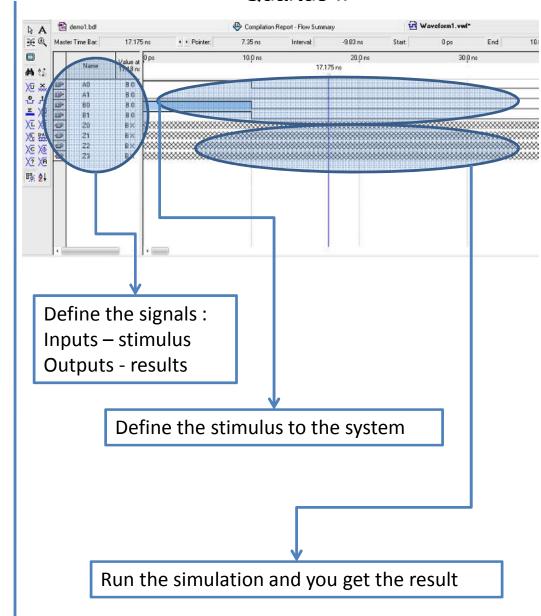

## **Tools - Simulation**

## Verilog

#### Example - Muy System Tasks & Functions Quartus II support for system tasks and functions is described below. So Description Language Based on the Verilog Hardware Description Language Verilog HDL Quartus II Support Note Section Construct (1) Display System Tasks Not supported. 14.1 File Input-Output 14.2 Not supported. System Tasks 14.3 Timescale System Not supported. Tasks Simulation Control Not supported. 14.4 System Tasks Timing Check System 14.5 Not supported. Tasks PLA Modeling System 14.6 Not supported. Tasks Stochastic Analysis Not supported. 14.7 System Tasks Simulation Time Not supported. 14.8 System Functions 14.9 Conversion Functions Not supported. for Reals Probabilistic. Not supported. 14.10 Distribution Functions

#### Quartus II

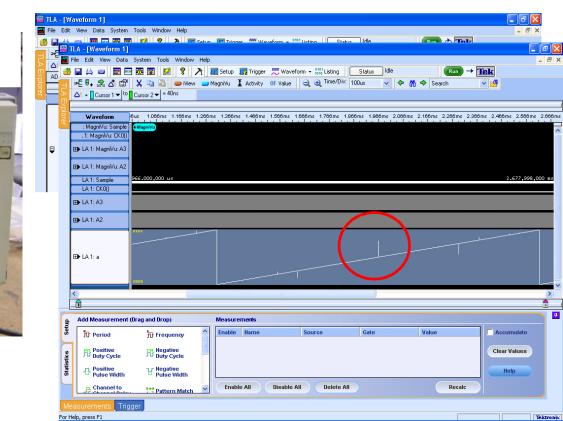

## Tools – Measurement instruments

## Waveforms

## Logic Levels

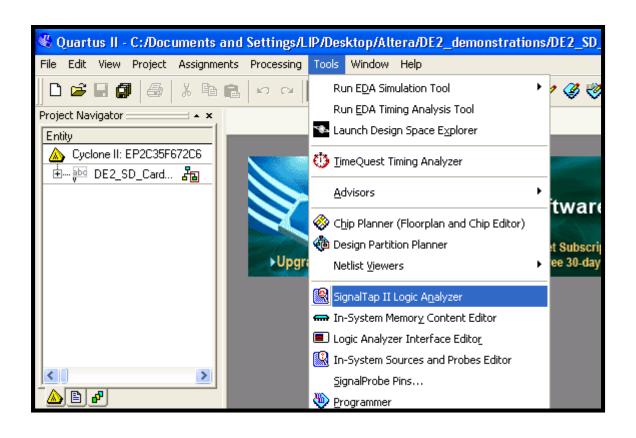

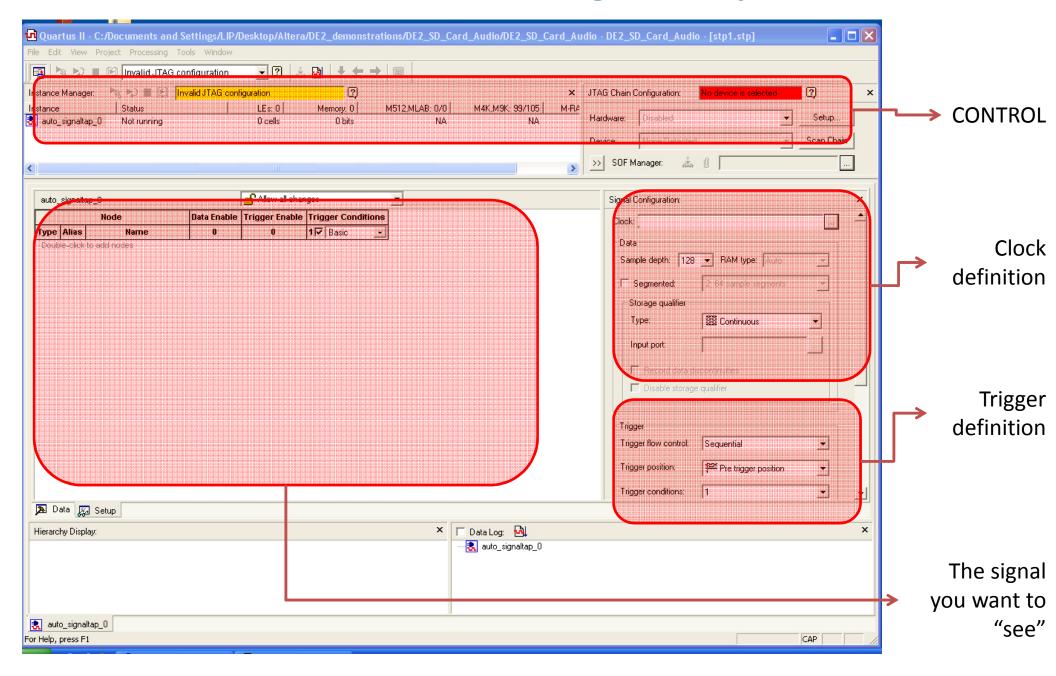

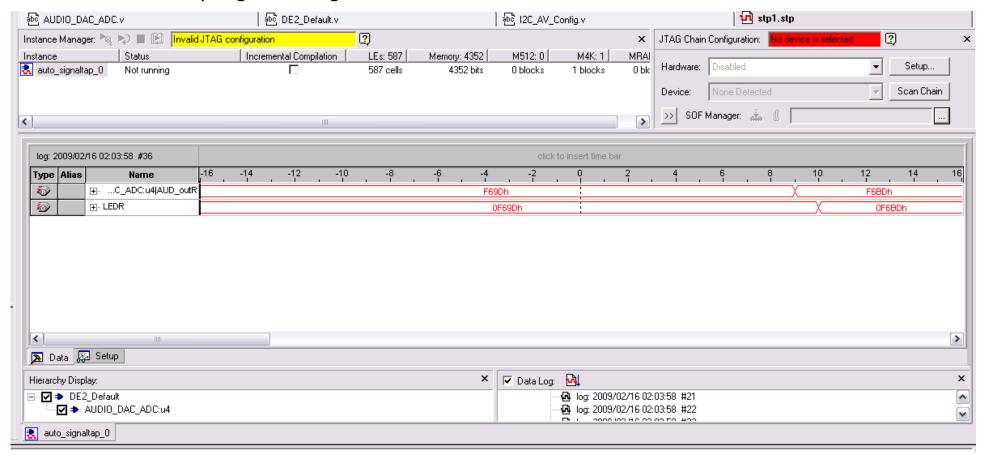

# Tools – Internal Logic Analyser

Signal-TAP embedded Logic Analyser

Quartus II Handbook Version 9.0 Volume 3: Verification 14. Design Debugging Using the SignalTap II Embedded Logic Analyzer

# Tools – Internal Logic Analyser

# Tools – Internal Logic Analyser

The logic analyser will collect data from the registers and output it through the JTAG programming interface

## Tools – Signal probe

Internal signals can be extracted to output pins and connected to na external logic analyser. Signals can be exchanged easily...

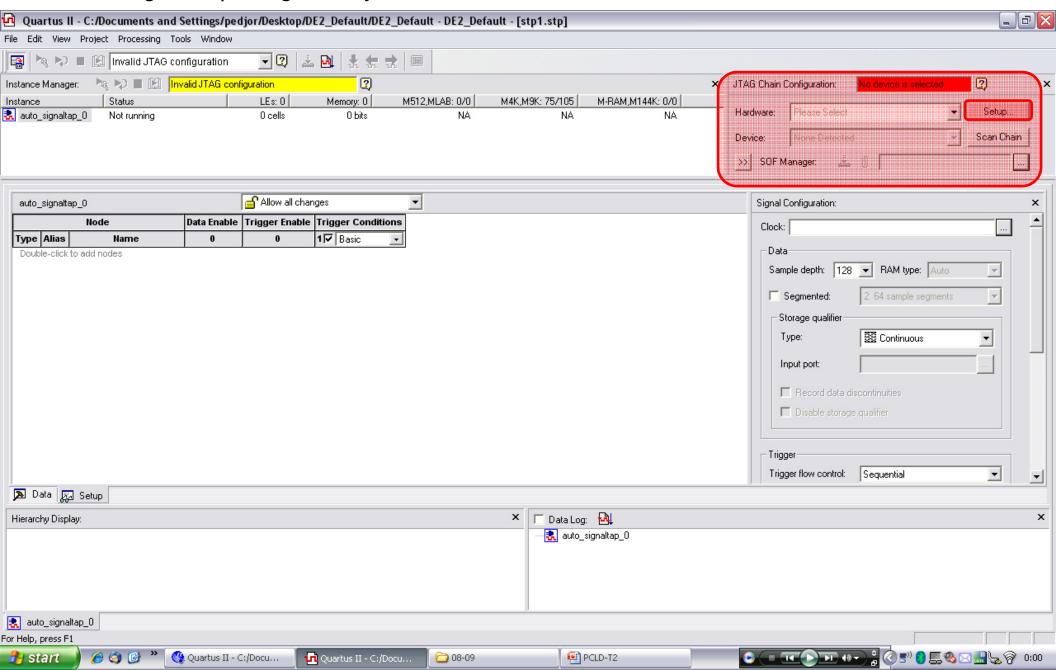

# SignalTap step by step

- •Open DE2 default and compile it!

- Program DE2

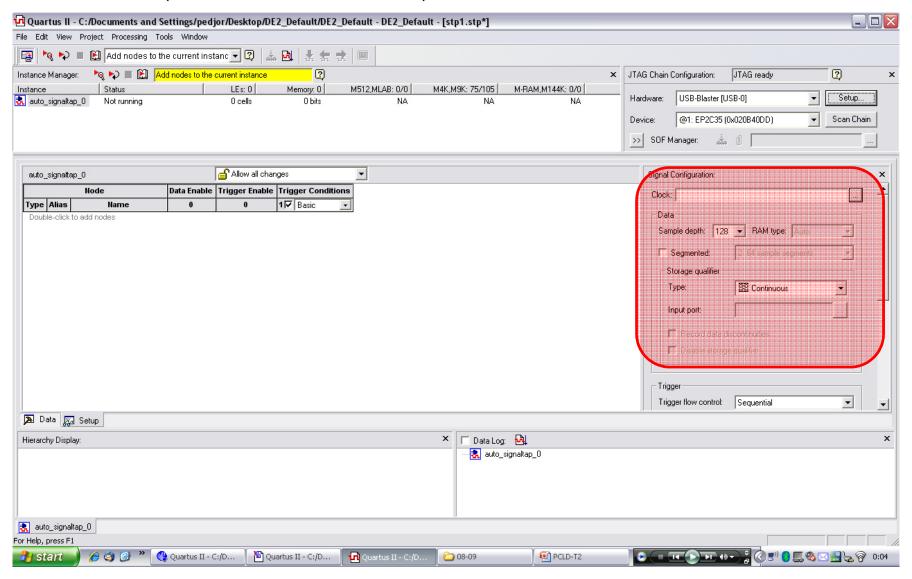

- Tools→Signal TapII Logic Analyser

Setup the hardware (choose the USB blaster)

Define the clock

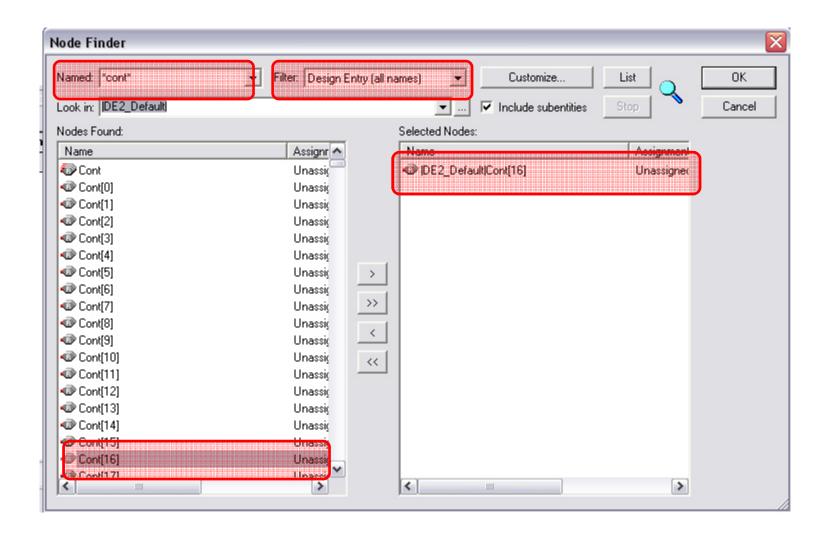

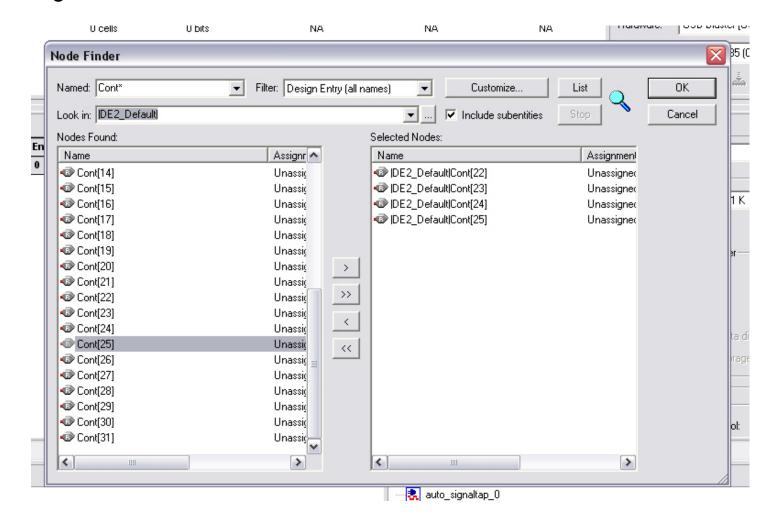

## Choose the signals to observe. Choose Cont 25,24,23,22

- •Compile the project! You may need to save some files and answer some questions

- •Program the board

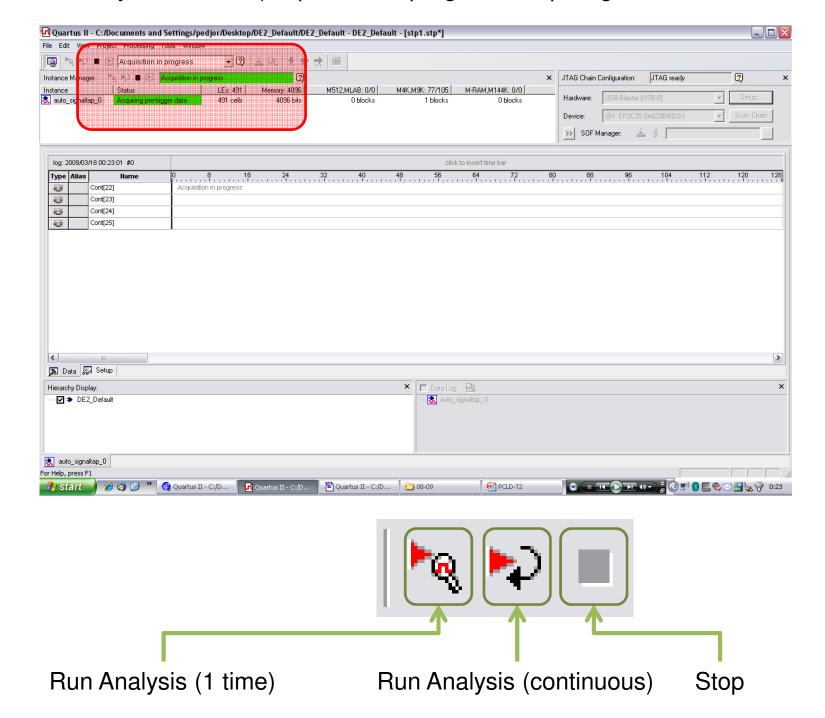

## Run Analysis -> Green (acquisition in progress, acquiring data

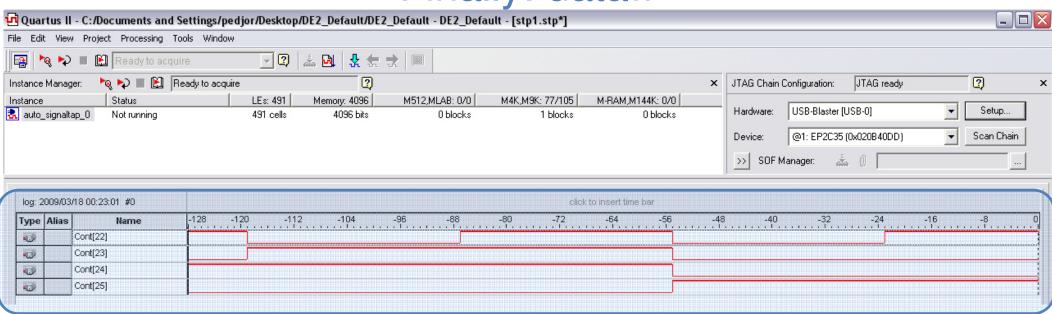

# Finally: data!!

- Select the four signals;

- •Edit → group

| log        | g: 200 | 09/03/ | 18 00:23:01 #0 | click to insert time bar |        |      |         |         |     |     |          |     |     |     |     |     |      |

|------------|--------|--------|----------------|--------------------------|--------|------|---------|---------|-----|-----|----------|-----|-----|-----|-----|-----|------|

| Тур        | oe A   | Alias  |                | -128 -12<br>             | 0 -112 | -104 | -96<br> | -88 -80 | -72 | -64 | -56<br>l | -48 | -40 | -32 | -24 | -16 | -8 0 |

| <b>(3)</b> | 2      |        | ⊕- Cont[2225]  | 5h                       | X 6h X |      | Χ       | (       |     |     |          | 8h  | Х   | 9h  |     |     |      |

- Select the group

- Edit→Bus Display Format→Unsigned Line Chart

| log: | 2009/03/ | M8 00:23:01 #0 |         | click to insert time bar |        |         |             |     |     |     |     |     |     |     |     |      |

|------|----------|----------------|---------|--------------------------|--------|---------|-------------|-----|-----|-----|-----|-----|-----|-----|-----|------|

| Туре | Alias    | Name           | -128 -1 | 120 -11                  | 2 -104 | -96<br> | -88 -80<br> | -72 | -64 | -56 | -48 | -40 | -32 | -24 | -16 | -8 ( |

| •    |          | ⊞- Cont[2225]  |         |                          |        |         |             |     |     |     |     |     |     |     |     |      |

#### •Unzoom

| log: 2   | 2009/03/ | 18 00:23:01 #0 |      |     |      |     |     |     | clic | k to insert time | e bar |     |     |     |     |     |     |     |

|----------|----------|----------------|------|-----|------|-----|-----|-----|------|------------------|-------|-----|-----|-----|-----|-----|-----|-----|

| Туре     | Alias    | Name           | -128 | -64 | 0 64 | 128 | 192 | 256 | 320  | 384              | 448   | 512 | 576 | 640 | 704 | 768 | 832 | 896 |

| <i>€</i> |          | ⊞- Cont[2225]  |      |     |      |     |     |     |      |                  |       |     |     |     |     |     |     |     |