# Projecto e Controlo em Lógica Digital

www.lip.pt/~pedjor/PCLD

- Microprocessors

- ·I/O

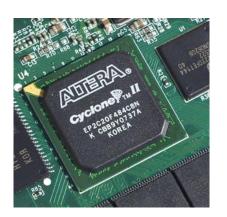

- •The FPGA

#### **Refs:**

Cyclone II device Handbook, Altera corp.

Quartus II Handbook, Altera corp.

DE2 documentation

Verilog HDL, S. Palnitkar, Prentice Hall

### Notes on our VGA

```

Colors module

module Colors(input hcount, vcount output [9:0]R, [9:0] G, [9:0] B);

Always @ (*)

if (hcount < 20)

R=

G=

B=

```

```

Or, in our application...

Reg [7:0] pos [7:0]; //this can be implemented as RAM

Pos={0,0,1,2,3,4,5,4,3,2,1,2,3,4,5,6,7,6,5,4,3,2,1,2,3,4,5,6.....}

If (hcount < 256 && vcount <256) //define a square to draw data if (vcount == pos [hcount]

RGB = "white" else "put black"

```

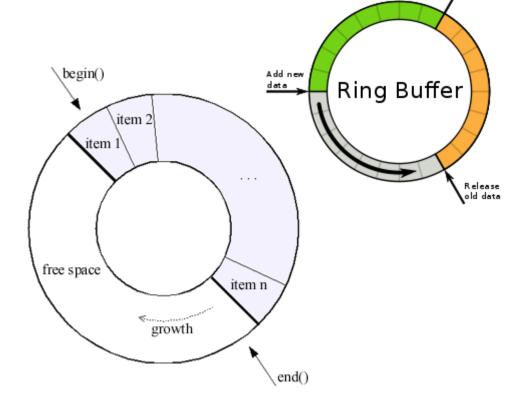

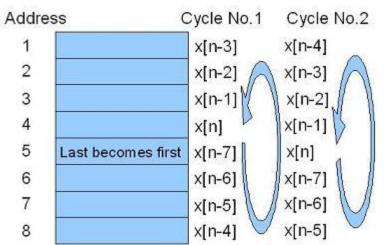

# The FIFO vs Ring memory

First-in First-out (FIFO)

Fetch data

$\mu P$

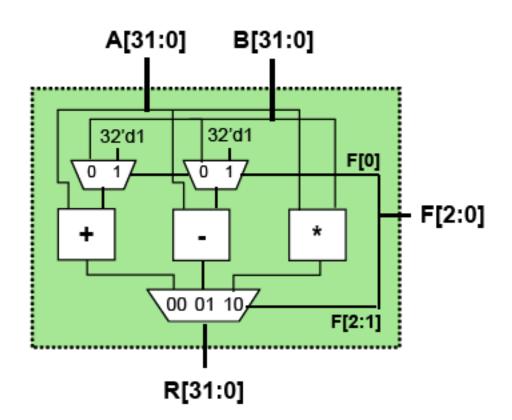

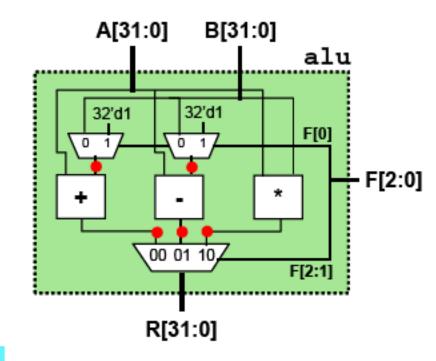

## Our ALU ... Or ... A simple CPU

- Modularity is essential to the success of large designs

- A Verilog module may contain submodules that are "wired together"

- High-level primitives enable direct synthesis of behavioral descriptions (functions such as additions, subtractions, shifts (<< and >>), etc.

### Example: A 32-bit ALU

## Function Table

| F2 | F1 | F0 | Function |  |  |

|----|----|----|----------|--|--|

| 0  | 0  | 0  | A + B    |  |  |

| 0  | 0  | 1  | A + 1    |  |  |

| 0  | 1  | 0  | A - B    |  |  |

| 0  | 1  | 1  | A - 1    |  |  |

| 1  | 0  | X  | A * B    |  |  |

|    |    |    | l        |  |  |

### Modules

#### 2-to-1 MUX

```

module mux32two(10,11,sel,out);

input [31:0] 10,11;

input sel;

output [31:0] out;

assign out = sel ? 11 : 10;

endmodule

```

#### 3-to-1 MUX

```

module mux32three(10,11,12,sel,out);

input [31:0] 10,11,12;

input [1:0] sel;

output [31:0] out;

reg [31:0] out;

always @ (10 or 11 or 12 or sel)

begin

case (sel)

2'b00: out = 10;

2'b01: out = 11;

2'b10: out = 32'bx;

endcase

end

endmodule

```

#### 32-bit Adder

```

module add32(10,11,sum);

input [31:0] 10,11;

output [31:0] sum;

assign sum = 10 + 11;

endmodule

```

#### 32-bit Subtracter

```

module sub32(10,11,diff);

input [31:0] 10,11;

output [31:0] diff;

assign diff = 10 - 11;

endmodule

```

#### 16-bit Multiplier

```

module mul16(i0,i1,prod);

input [15:0] i0,i1;

output [31:0] prod;

// this is a magnitude multiplier

// signed arithmetic later

assign prod = 10 * i1;

endmodule

```

## Top-Level: connect the modules

#### Given submodules:

```

module mux32two(10,11,sel,out);

module mux32three(10,11,12,sel,out);

module add32(10,11,sum);

module sub32(10,11,diff);

module mul16(10,11,prod);

```

#### Declaration of the ALU Module:

wire [31:0] addmux out, submux out;

module

names

```

module alu(a, b, f, r);

input [31:0] a, b;

input [2:0] f;

output [31:0] r;

```

```

wire [31:0] add_out, sub_out, mul_out;

mux32two adder_mux(b, 32'd1, f[0], addmux_out);

mux32two sub_mux(b, 32'd1, f[0], submux_out);

add32 our adder(a, addmux out, add out);

```

our subtracter (a, submux out, sub out);

our multiplier (a[15:0], b[15:0], mul out);

mux32three output\_mux(add\_out, sub\_out, mul\_out, f[2:1], r);

endmodule

sub32

(unique) instance names corresponding wires/regs in module alu

intermediate output nodes 👨

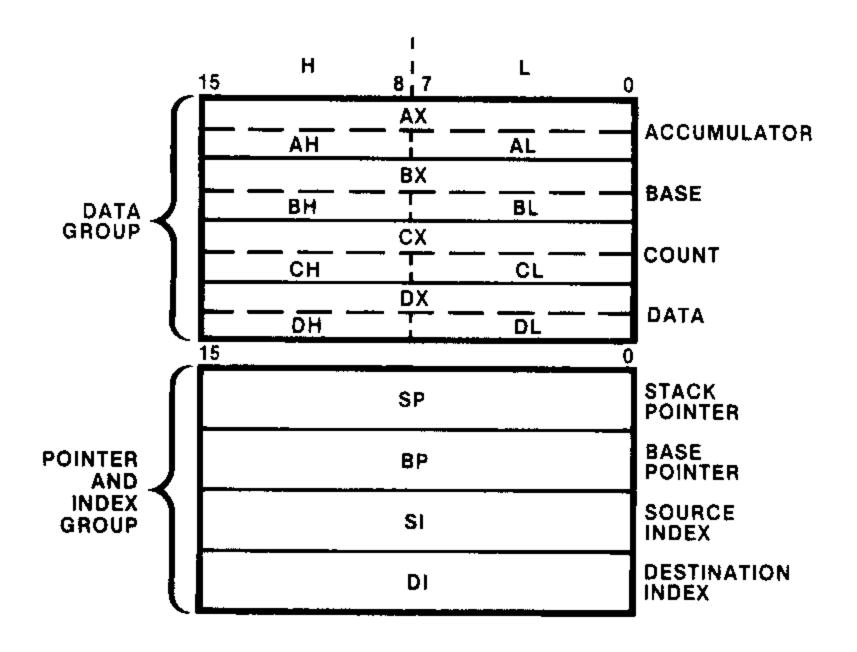

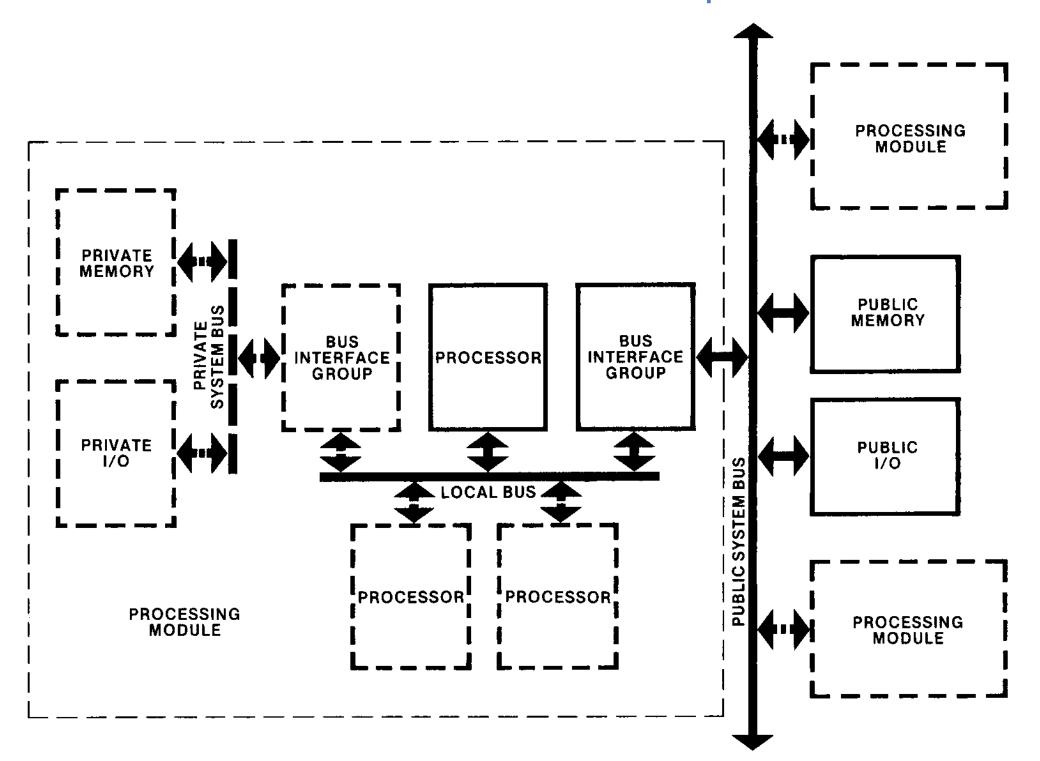

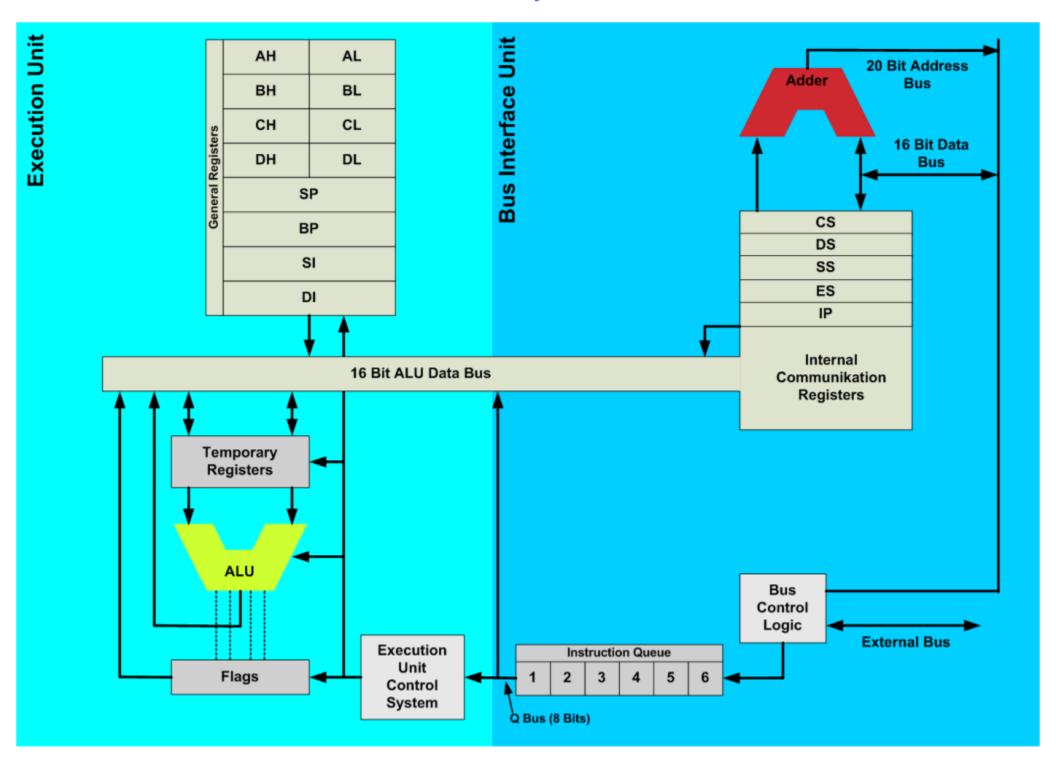

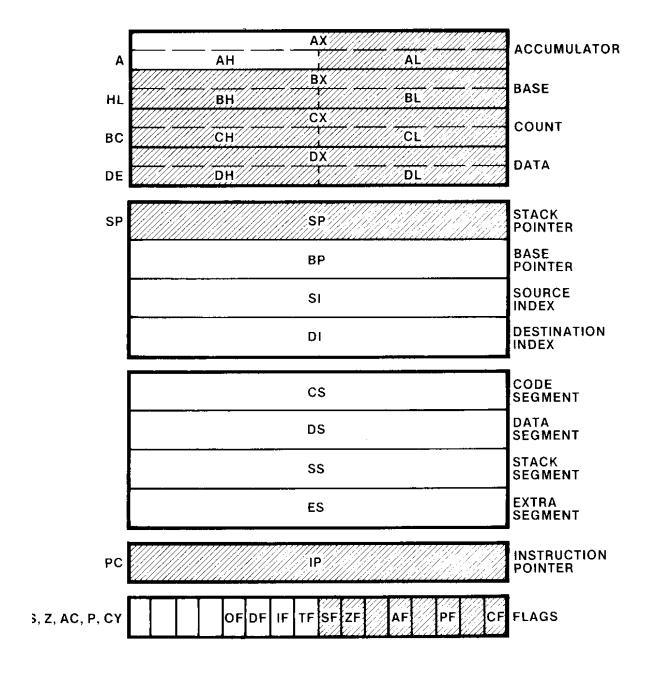

## The 8086 Family User's Manual

October 1979

## The Processor in a computer

## Inside the processor

## Instructions and Data

Figure 2-10. 8080/8085 Register Subset (Shaded)

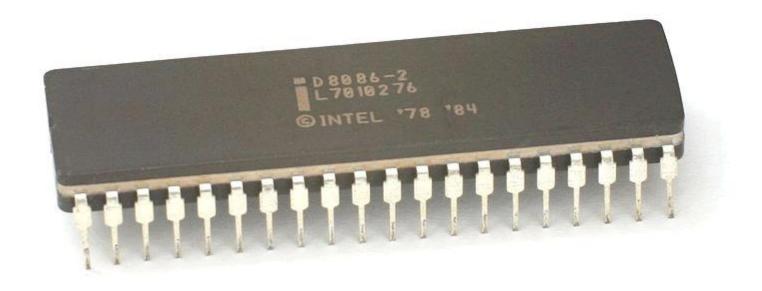

# ... all packed in a DIP

# How to give instructions?

| 15  | 1ST BYTE |      | 2ND BYTE    | BYTES 3, 4, 5, 6    | ASM-86 INSTRUCTION FORMAT |                   |  |

|-----|----------|------|-------------|---------------------|---------------------------|-------------------|--|

| HEX | BIN      | ARY  | ZNDBITE     | D11E00, 4, 5, 0     | AOIII-0                   |                   |  |

| 00  | 0000     | 0000 | MOD REG R/M | (DISP-LO),(DISP-HI) | ADD                       | REG8/MEM8,REG8    |  |

| 01  | 0000     | 0001 | MOD REG R/M | (DISP-LO),(DISP-HI) | ADD                       | REG16/MEM16,REG16 |  |

| 02  | 0000     | 0010 | MOD REG R/M | (DISP-LO),(DISP-HI) | ADD                       | REG8,REG8/MEM8    |  |

| 03  | 0000     | 0011 | MOD REG R/M | (DISP-LO),(DISP-HI) | ADD                       | REG16,REG16/MEM16 |  |

| 04  | 0000     | 0100 | DATA-8      |                     | ADD                       | AL,IMMED8         |  |

| 05  | 0000     | 0101 | DATA-LO     | DATA-HI             | ADD                       | AX,IMMED16        |  |

| 06  | 0000     | 0110 |             |                     | PUSH                      | ES                |  |

| 07  | 0000     | 0111 |             |                     | POP                       | ES                |  |

ASSEMBLER IS ALREADY A PROGRAMMING LANGUAGE...

FIRST ABSTRACTION LEVEL!

## The Instruction set

| \    | Lo                |                 |                |                 |               |               |                |                |                |                |                  |                |                 |               |                  |                |

|------|-------------------|-----------------|----------------|-----------------|---------------|---------------|----------------|----------------|----------------|----------------|------------------|----------------|-----------------|---------------|------------------|----------------|

| Hi \ | 0                 | 1               | 2              | 3               | 4             | 5             | 6              | 7              | 8              | 9              | A                | В              | C               | 0             | E                | F              |

| 0    | ADD<br>b,f,r/m    | ADD<br>w.f.r/m  | ADD<br>b,t,r/m | ADD<br>w,t,r/m  | ADD<br>b, ia  | ADD<br>w.ia   | PUSH<br>ES     | POP<br>ES      | OR<br>b,f,r/m  | OR<br>w,f,r/m  | OR<br>b,t,r/m    | OR<br>w,t,r/m  | OR<br>b.i       | OR<br>W.i     | PUSH<br>CS       | <u> </u>       |

| 1    | ADC<br>b,f,r/m    | ADC<br>w.f.r/m  | ADC<br>b,t,r/m | ADC<br>w,t,r/m  | ADC<br>b,i    | ADC<br>w,i    | PUSH<br>SS     | POP<br>SS      | SBB<br>b,f,r/m | SBB<br>w,f,r/m | SBB<br>b,t,r/m   | SBB<br>w.t,r/m | SBB<br>b.i      | SBB           | PUSH<br>DS       | POP<br>DS      |

| 2    | AND<br>b,f,r/m    | AND<br>w.f.r/m  | AND<br>b,t,r/m | AND<br>w,t,r/m  | AND<br>b,i    | AND<br>w,i    | SEG<br>=ES     | DAA            | SUB<br>b,f,r/m | SUB<br>w,f,r/m | SUB<br>b.t,r/m   | SUB<br>w,t,r/m | SUB<br>b,i      | SUB           | SEG<br>CS        | DAS            |

| 3    | XOR<br>b,f,r/m    | XOR<br>w.f.r/m  | XOR<br>b,t,r/m | XOR<br>w,t,r/m  | XOR<br>b.i    | XOR<br>w,i    | SEG<br>=SS     | ААА            | CMP<br>b.f.r/m | CMP<br>w.f.r/m | CMP<br>b,t,r/m   | CMP<br>w,t,r/m | CMP<br>b,i      | CMP           | SEG              | AAS            |

| 4    | INC<br>AX         | INC<br>CX       | INC<br>DX      | INC<br>BX       | INC<br>SP     | INC<br>BP     | INC<br>SI      | INC<br>DI      | DEC<br>AX      | DEC<br>CX      | DEC<br>DX        | DEC<br>BX      | DEC<br>SP       | DEC<br>BP     | DEC              | DEC<br>Di      |

| 5    | PUSH<br>AX        | PUSH<br>CX      | PUSH<br>DX     | PUSH<br>BX      | PUSH<br>SP    | PUSH<br>BP    | PUSH<br>Si     | PUSH<br>DI     | POP<br>AX      | POP<br>CX      | POP<br>DX        | POP<br>BX      | POP<br>SP       | POP<br>BP     | POP<br>SI        | POP<br>DI      |

| 6    |                   |                 |                | 1               |               |               |                |                |                |                |                  | <u> </u>       | <u> </u>        |               | 31               | יט             |

| 7    | J0                | JNO             | JB/<br>JNAE    | JNB/<br>JAE     | JE/<br>JZ     | JNE/<br>JNZ   | JBE/<br>JNA    | JNBE/<br>JA    | JS             | JNS            | JP/<br>JPE       | JNP/<br>JP0    | JL/<br>JNGE     | JNL/          | JLE/             | JNLE/          |

| 8    | Immed<br>b,r/m    | Immed<br>w,r/m  | lmmed<br>b,r/m | Immed<br>is,r/m | TEST<br>b,r/m | TEST<br>w,r/m | XCHG<br>b,r/m  | XCHG<br>w.r/m  | MOV<br>b,f,r/m | MOV<br>w,f.r/m | MOV<br>b,t,r/m   | MOV<br>w,t,r/m | MOV<br>sr,f,r/m | JGE<br>LEA    | JNG<br>MOV       | JG<br>POP      |

| 9    | XCHG<br>AX        | XCHG<br>CX      | XCHG<br>DX     | XCHG<br>BX      | XCHG<br>SP    | XCHG<br>BP    | XCHG<br>SI     | XCHG<br>DI     | CBW            | CWD            | CALL<br>I,d      | WAIT           | PUSHF           | POPF          | sr,t,r/m<br>SAHF | r/m<br>LAHF    |

| A    | MOV<br>m - AL     | MOV<br>m → AX   | MOV<br>AL → m  | M0V<br>AX → m   | MOVS          | MOVS          | CMPS           | CMPS           | TEST<br>b,l,a  | TEST<br>w,i,a  | STOS             | STOS           | LODS            | LODS          | SCAS             | SCAS           |

| B    | MOV<br>r AL       | MOV<br>i → CL   | MOV<br>i → DL  | MOV<br>i → BL   | MOV<br>i AH   | MOV<br>i CH   | MOV<br>i → DH  | MOV<br>i BH    | MOV<br>i – AX  | MOV<br>i — CX  | MOV<br>i – DX    | MOV<br>I — BX  | MOV<br>I - SP   | MOV<br>i → BP | MOV<br>i — SI    | MOV<br>i - DI  |

| C    |                   |                 | RET,<br>(i+SP) | RET             | LES           | LDS           | MOV<br>b,i,r/m | MOV<br>w,i.r/m | -              |                | RET,<br>I,(i+SP) | RET            | INT<br>Type 3   | INT<br>(Any)  | INTO             | IRET           |

| 0    | Shift<br>b        | Shift<br>w      | Shift<br>b,v   | Shift<br>w,v    | AAM           | AAD           |                | XLAT           | ESC<br>0       | ESC<br>1       | ESC 2            | ESC<br>3       | ESC<br>4        | ESC<br>5      | ESC<br>6         | ESC            |

| E    | LOOPNZ/<br>LOOPNE | LOOPZ/<br>LOOPE | LOOP           | JCXZ            | IN<br>b       | IN<br>W       | OUT            | OUT<br>W       | CALL           | JMP<br>d       | JMP<br>I,d       | JMP<br>si,d    | IN<br>v,b       | IN<br>V,W     | OUT<br>v,b       | 7<br>OUT       |

| F    | LOCK              |                 | REP            | REP<br>Z        | HLT           | СМС           | Grp 1<br>b,r/m | Grp 1<br>w.r/m | CLC            | STC            | CLI              | STI            | CLD             | STD           | Grp 2            | Grp 2<br>w.r/m |

# The definition of Instructions... Two examples

| ADD                    | ADD destination, so<br>Addition | ource      | Flags ODITSZAPC |                    |  |  |

|------------------------|---------------------------------|------------|-----------------|--------------------|--|--|

| Operands               | Clocks                          | Transfers* | Bytes           | Coding Example     |  |  |

| register, register     | 3                               | _          | 2               | ADD CX, DX         |  |  |

| register, memory       | 9 + EA                          | 1          | 2-4             | ADD DI, [BX].ALPHA |  |  |

| memory, register       | 16 + EA                         | 2          | 2-4             | ADD TEMP, CL       |  |  |

| register, immediate    | 4                               | _          | 3-4             | ADD CL, 2          |  |  |

| memory, immediate      | 17 + EA                         | 2          | 3-6             | ADD ALPHA, 2       |  |  |

| accumulator, immediate | 4                               | ı          | 2-3             | ADD AX, 200        |  |  |

| AND                                                                                                                              | AND destination,<br>Logical and        | source     | Flags ODITSZAPC XXUX0                |                                                                                          |  |  |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------|--------------------------------------|------------------------------------------------------------------------------------------|--|--|

| Operands                                                                                                                         | Clocks                                 | Transfers* | Bytes                                | Coding Example                                                                           |  |  |

| register, register<br>register, memory<br>memory, register<br>register, immediate<br>memory, immediate<br>accumulator, immediate | 3<br>9 + EA<br>16 + EA<br>4<br>17 + EA | 2          | 2<br>2-4<br>2-4<br>3-4<br>3-6<br>2-3 | AND AL,BL AND CX,FLAG_WORD AND ASCII [DI],AL AND CX,0F0H AND BETA, 01H AND AX, 01010000B |  |  |

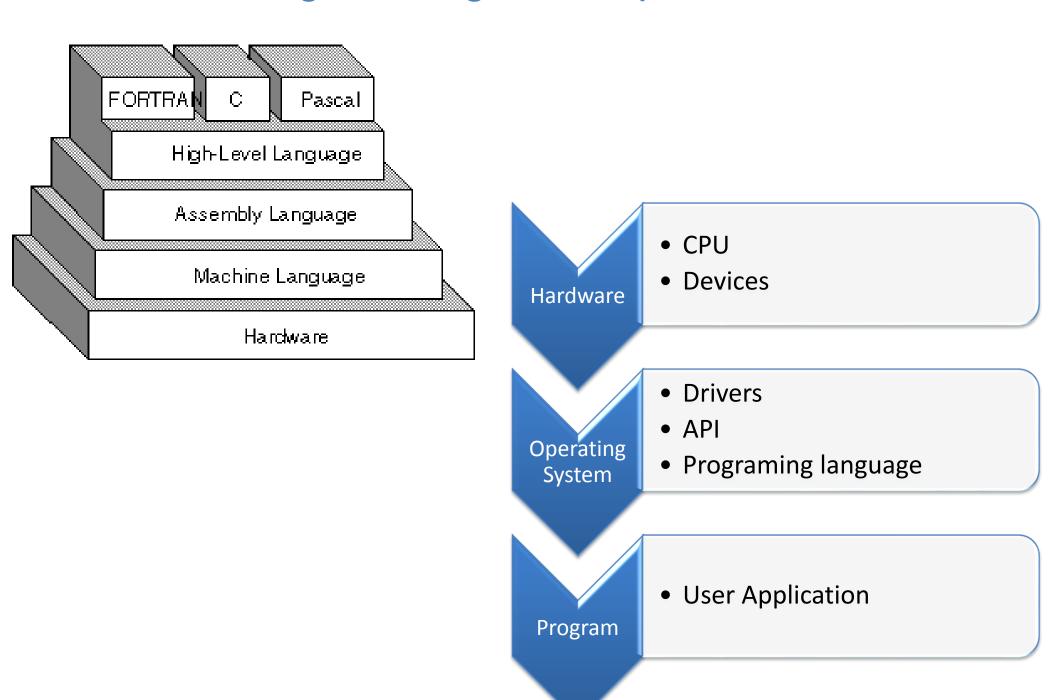

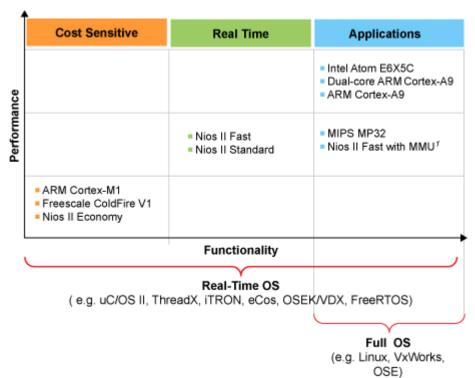

## Programming a microprocessor

## Programming a microprocessor

**ARM**

**ARM**

### The ALTERA "standard"

Lots of tools and tutorials...

e.g. NIOS IDE (Integrated Development Environment)

DE2 demonstrations

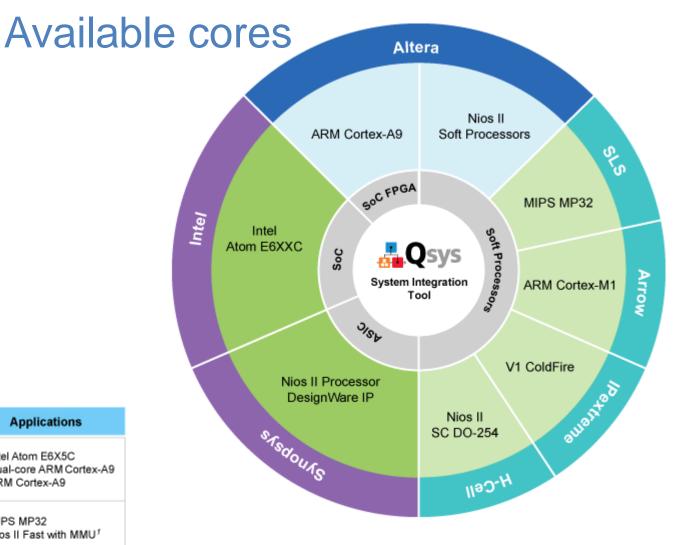

## Tools – SOPC builder

http://www.altera.com/education/demonstrations/sopc-builder/sopc-builder-demo.html

ftp://ftp.altera.com/up/pub/Tutorials/DE2/Computer\_Organization/tut\_sopc\_introduction\_verilog.pdf

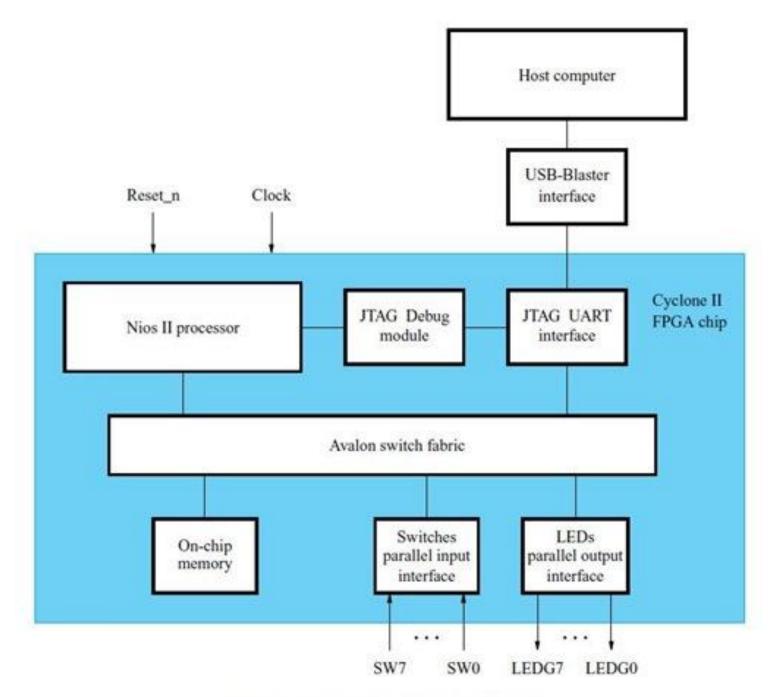

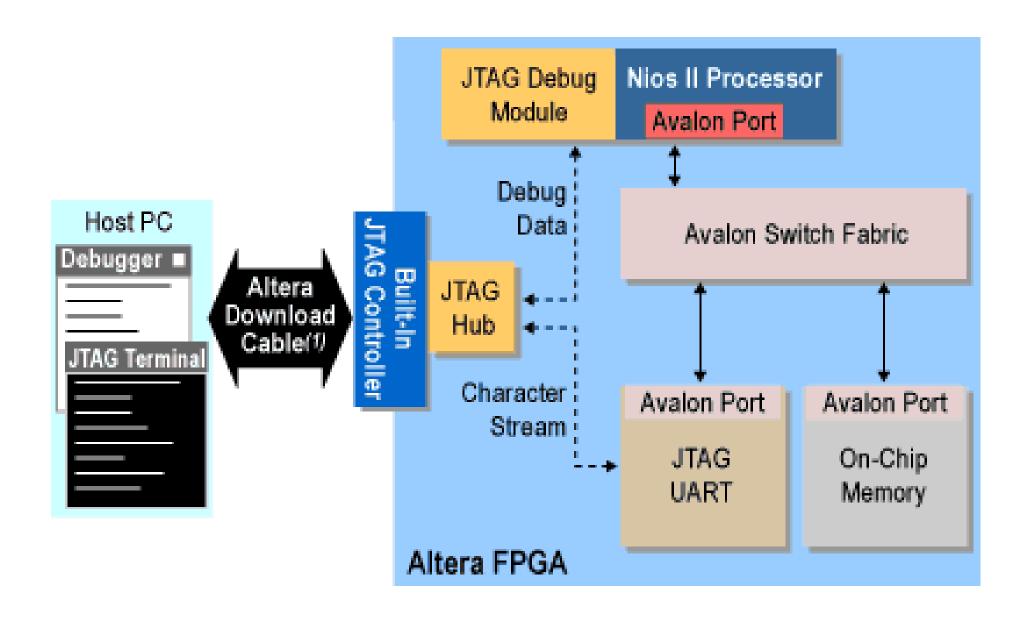

The SOPC Builder is a tool used in conjuction with the Quartus II CAD software. It allows the user to easily create a system based on the Nios II processor, by simply selecting the desired functional units and specifying their parameters.

There are other choices of µ-processors to implements. E.g.: mips Operating systems can be used. E.g. µ-Clinux™

Figure 2. A simple example of a Nios II system.

## **JTAG Debug Module**

## Tools - Mega Wizard

ftp://ftp.altera.com/up/pub/Tutorials/DE2/Digital\_Logic/tut\_lpms\_verilog.pdf

### Tools – SOPC builder

http://www.altera.com/education/demonstrations/sopc-builder/sopc-builder-demo.html

<u>ftp://ftp.altera.com/up/pub/Tutorials/DE2/Computer\_Organization/tut\_sopc\_introduction\_verilog.pdf</u>

The SOPC Builder is a tool used in conjuction with the Quartus II CAD software. It allows the user to easily create a system based on the Nios II processor, by simply selecting the desired functional units and specifying their parameters.

## Tools - QSys

QSys is currently replacing SOPC builder in newer versions of Altera's software. Some Quartus versions will ask you to use this new tool!

# I/O

Interfaces to the outside world

## I/O - parallel

Parallel protocols are tipically easy and fast...

However the resources alocated are big (pins)

Tipycally the protocol language is very easy.

Time constraints easy to deal with

e.g.: GPIO

## I/O - parallel

Parallel protocols are tipically easy and fast...

However the resources alocated are big (pins)

Tipycally the protocol language is very easy.

Time constraints easy to deal with

e.g.: The PCI protocol

### I/O - serial

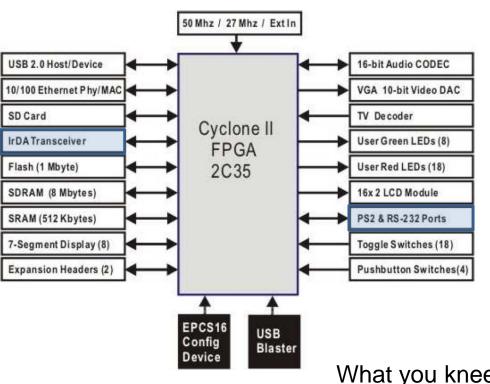

Readily available: IrDA, RS232, PS2

You can build some other... 12C - Inter-Integrated Circuit Serial Peripheral Interface (SPI)

What you kneed to know?

- Pinout

- Clocking requirements

- Protocol (the language)

- •The commands of the peripherical you are communicating with

- A zillion standards

- Asynchronous (no explicit clock) vs. Synchronous (CLK line in addition to DATA line).

- Recent trend to reduce signaling voltages: save power, reduce transition times

- Control/low-bandwidth Interfaces: SPI, I<sup>2</sup>C, 1-Wire, PS/2, AC97

- Networking: RS232, Ethernet, T1, Sonet

- Computer Peripherals: USB, FireWire, Fiber Channel, Infiniband, SATA, Serial Attached SCSI

## RS232 – The serial port

#### Characteristics

- Large voltages => special interface chips

(1/mark: -12V to -3V, O/space: 3V to 12V)

- Separate xmit and rcv wires: full duplex

- Slow transmission rates (1 bit time = 1 baud); most interfaces support standardized baud rates: 1200, 2400, 4800, 9600, 19.2K, 38.4K, 57.6K, 115.2K

- Format

- Wire is held at 1/mark when idle

- Start bit (1 bit of "0" at start of transmission)

- Data bits (LSB first, can be 5 to 8 bits of data)

- Parity bit (none, even, odd)

- Stop bits (1, 1.5 or 2 bits of 1/mark at end of symbol)

- Most common 8-N-1: eight data bits, no parity, one stop bit

Sending: easy - Just compose your signal respecting time constraints Receiving: Need to oversample and understand where the bits are... and check the protocol format: start, stop, parity

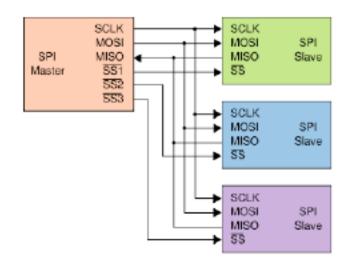

# SPI (Serial Peripheral Interface)

- Simple, 3-wire interface + devices selects

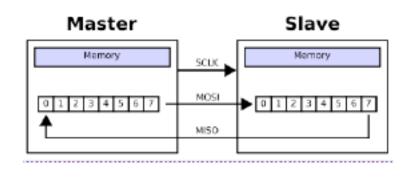

- SCLK generated by master (1-70MHz). Assert data on one edge, sample data on the other. Default state of SCLK and assignment of edges is often programmable.

- Master Out Slave In (MOSI) data shifted out of master register into slave register

- Master In Slave Out (MISO) data shifted out of slave register and into master register

- Selects (usually active low) determine which device is active.

Assertion often triggers an action in the slave, so master waits some predetermined time then shifts data.

Figures from Wikipedia

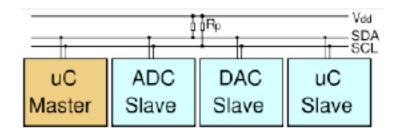

# I<sup>2</sup>C (Inter-Integrated Circuit)

- 2 open-drain wires (SCL = clock, SDA = data)

- Multiple-master, each transmission addresses a particular device, many devices have many different sub-addresses (internal registers)

- Format (all addresses/data send MSB first):

- Sender: Start [5] bit (SDA♥ while SCL high)

- Sender: One or more 8-bit data packets, each followed by 1-bit ACK

- Data changed when SCL low, sampled at SCL

- Receiver: Active-low ACK generated after each data packet

- Sender: Stop [P] bit (SDA↑ while SCL high)

- SCL and SDA have pullup resistors, senders only drive low, go high

-impedance to let pullups make line high (so multiple drivers okay!)

- Receiver can hold SCL low to stretch clock timing, sender must wait until SCL goes high before moving to next bit.

- Multiple senders can contend using SDA for arbitration

## Just two examples in a PC

#### Sensors like thermometers in the motherboard communicate using I2C

#### Most PCs have a "hidden I2C Port"

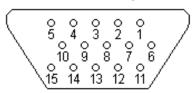

#### VGA DB15 connector pinout

The pin layout of the **VGA** interface connector is shown in the figure below. Three pins are used to carry the three basic **RGB** color signals *red*, *green* and *blue* and two pins carry the horizontal and vertical *sync* signal. The red, green and blue signal lines have their own ground return line. The picture shows the **VGA DDC2** connector including the **I2C SLC** clock and **SDA** data lines for exchanging digital data between the video controller and the display.

#### VGA connector pinout

| Pin | Name      | Function             |

|-----|-----------|----------------------|

| 1   | RED       | Red video            |

| 2   | GREEN     | Green video          |

| 3   | BLUE      | Blue video           |

| 4   | n/c       | not connected        |

| 5   | GND       | Signal ground        |

| 6   | RED_RTN   | Red ground           |

| 7   | GREEN_RTN | Green ground         |

| 8   | BLUE_RTN  | Blue ground          |

| 9   | VDC       | 5 VDC supply (fused) |

| 10  | GND       | Signal ground        |

| 11  | n/c       | not connected        |

| 12  | SDA       | DDC / I2C data       |

| 13  | HSYNC     | Horizontal sync      |

| 14  | VSYNC     | Vertical sync        |

| 15  | SCL       | DDC / I2C clock      |

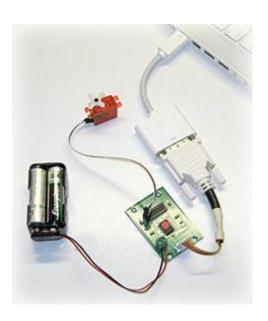

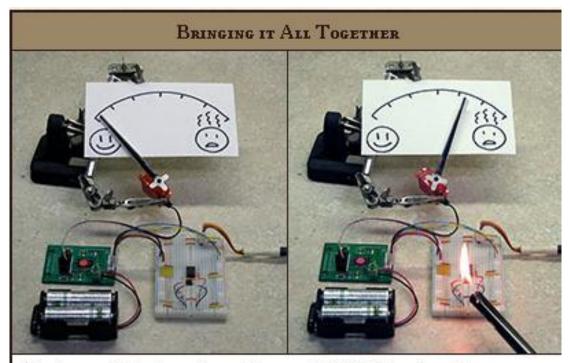

## THE 25¢ I<sup>2</sup>C ADAPTER

(http://www.paintyourdragon.com/?p=43)

Here's a quick test case involving multiple I<sup>2</sup>C devices: the computer (out of frame, to the right) reads the current temperature from a sensor, then updates a hobby servo being used as a makeshift dial indicator. The readings are also logged to EEPROM for posterity. The example code can do all of these functions, plus others.

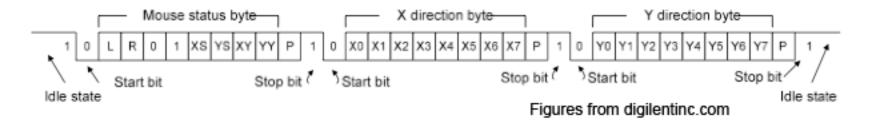

## PS/2 Keyboard/Mouse Interface

- 2-wire interface (CLK, DATA), bidirectional transmission of serial data at 10-16kHz

- Format

- Device generates CLK, but host can request-to-send by holding CLK low for 100us

- Tck Tck Edge 10

'0' start bit

Tsu + Thid

Tsu + Thid

- DATA and CLK idle at "1", CLK starts when there's a transmission. DATA changes on CLK♠, sampled on CLK♥

| Symbol           | Parameter                | Min  | Max  |

|------------------|--------------------------|------|------|

| T <sub>CK</sub>  | Clock time               | 30us | 50us |

| T <sub>SU</sub>  | Data-to-clock setup time | 5us  | 25us |

| T <sub>HLD</sub> | Clock-to-data hold time  | 5us  | 25us |

- 11-bit packets: one start bit of "0", 8 data bits (LSB first), odd parity bit, one stop bit of "1".

- Keyboards send scan codes (not ASCII!) for each press, 8'hFO followed by scan code for each release

- Mice send button status,  $\Delta x$  and  $\Delta y$  of movement since last transmission

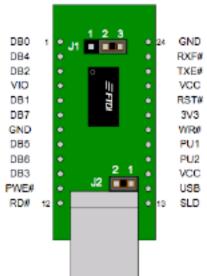

## USB (Universal Serial Bus)

- 2-wire (D+,D-) for high-speed, bidirectional polled transmission between master and addressable endpoints in multiple devices.

Full speed (12Mbps) and High speed (480Mbps) data rates.

- Multi-level tiered-star topology (127 devices, including hubs)

- FTDI UM245R USB-to-FIFO module for bidirectional data transfer using a handshake protocol, also asynchronous "bit -bang" mode with selectable baud rates.

- 24-pin DIP module, wire to user pins

Figures from ftdi.com

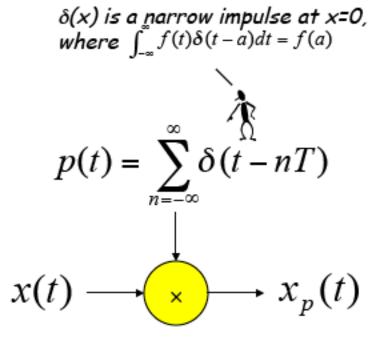

# I/O - Analog

#### PWM – Pulse Width Modulation

## I/O – Digital ⇔ Analog

FPGAs are digital devices!

They can't generate or receive analog signals.

You need to use a DAC or ADC to interface analog devices!

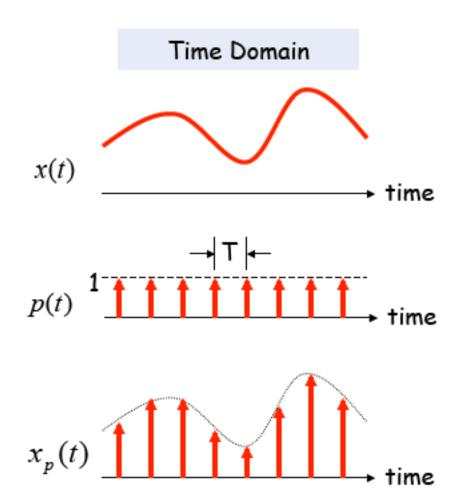

#### Discrete Time

Let's use an impulse train to sample a continuous-time function at a regular interval T:

#### Non-idealities in Data Conversion

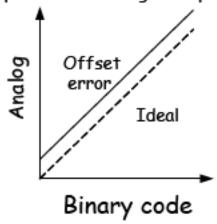

Offset - a constant voltage offset that appears at the output when the digital input is 0

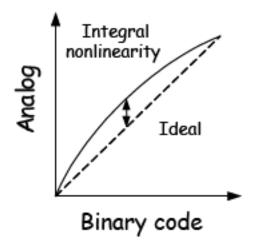

Integral Nonlinearity - maximum deviation from the ideal analog output voltage

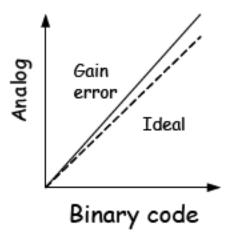

Gain error – deviation of slope from ideal value of 1

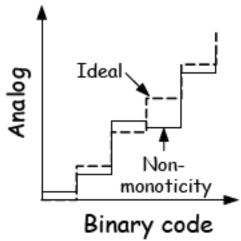

Differential nonlinearity - the largest increment in analog output for a 1-bit change

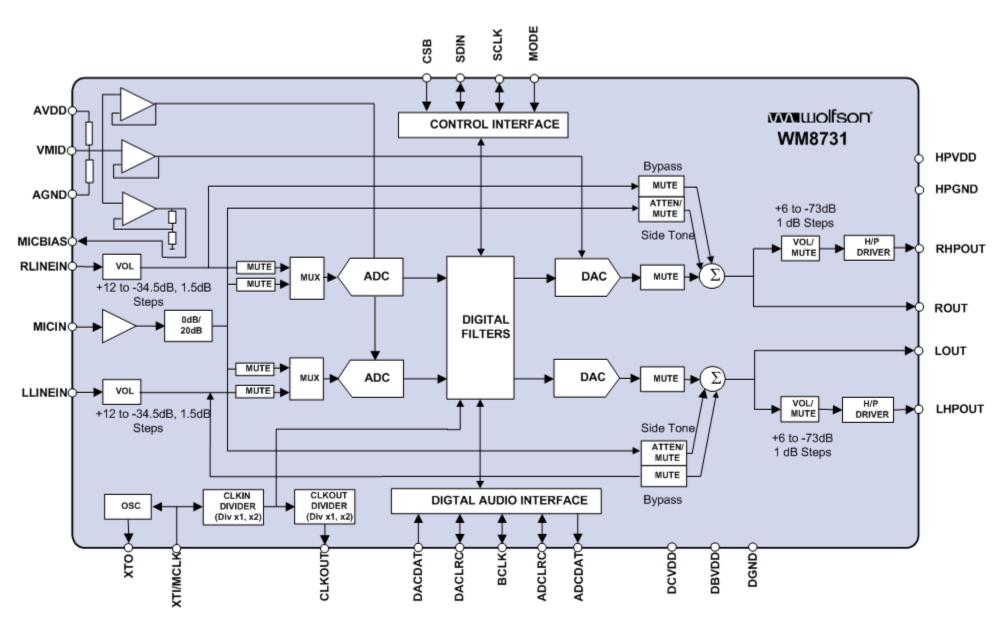

#### Sound (analog signal)

Means ADC/DAC

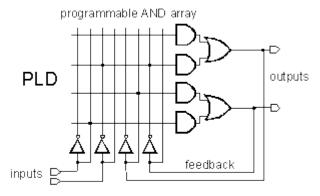

# Finally... What is an FPGA

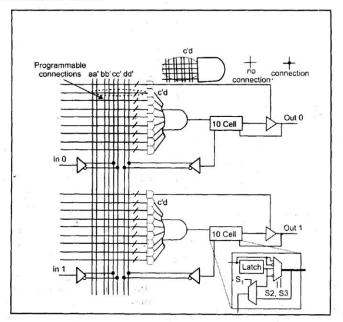

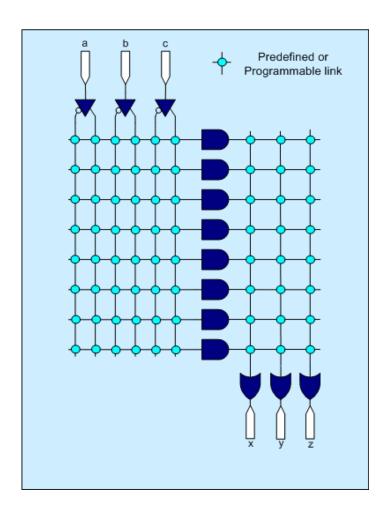

PLD Architecture

#### Architecture of CPLD:

Fig. Simple architecture of a CPLD.

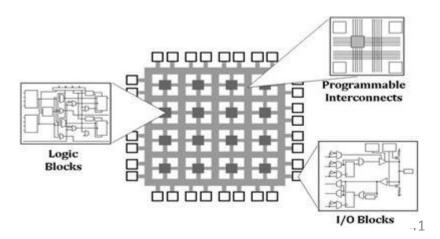

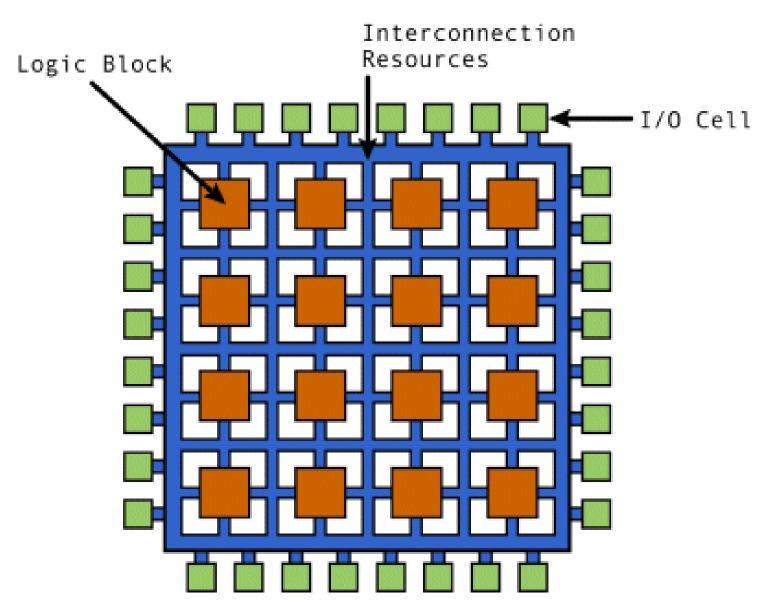

#### **FPGA**

Field Programmable Gate Array:

Set of Chips in a bread board.

Control:

Chips functions

Connections

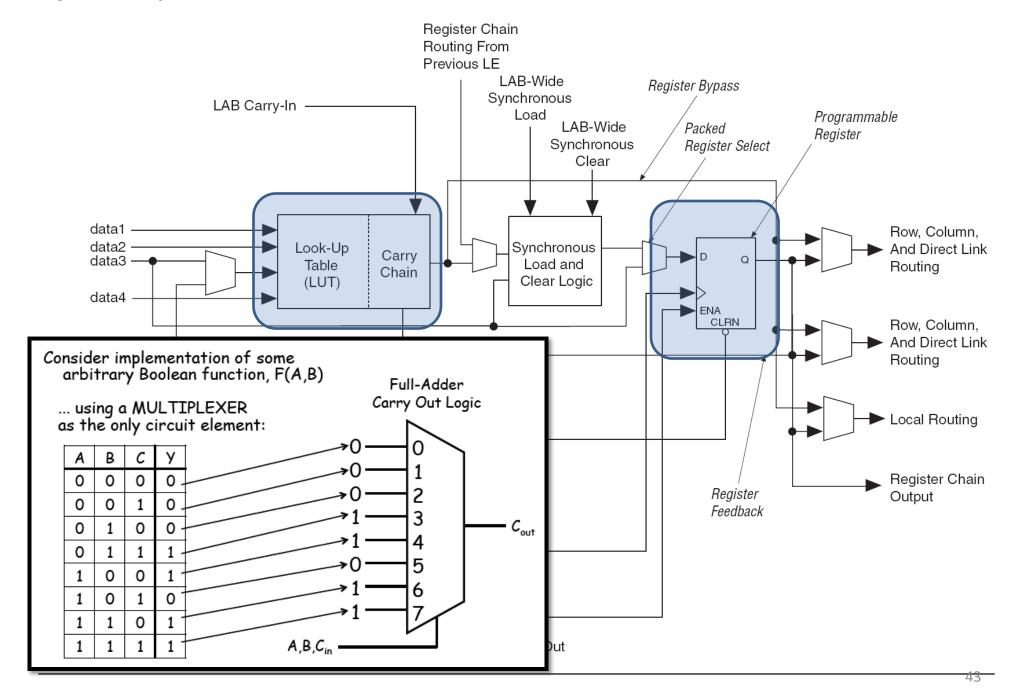

#### Logic elements

Figure 2-2. Cyclone II LE

#### **HDL**

Hardware

Description

Language

#### A Tale of Two HDLs

#### <u>VHDL</u>

ADA-like verbose syntax, lots of redundancy (which can be good!)

Extensible types and simulation engine. Logic representations are not built in and have evolved with time (IEEE-1164).

Design is composed of entities each of which can have multiple architectures. A configuration chooses what architecture is used for a given instance of an entity.

Behavioral, dataflow and structural modeling. Synthesizable subset...

Harder to learn and use, not technology-specific, DoD mandate

#### <u>Verilog</u>

C-like concise syntax

Built-in types and logic representations. Oddly, this led to slightly incompatible simulators from different vendors.

Design is composed of modules.

Behavioral, dataflow and structural modeling.

Synthesizable subset...

Easy to learn and use, fast simulation, good for hardware design

### Programação de microprocessadores

(assembly, c++, etc.)

Dar ao "gnomo" uma lista (consecutiva) de operações a realizar

1 Máquina executa várias tarefas consecutivas

## Programação de Lógica Digital

(FPGAs+HDL)

Dar ao gnomo uma lista de "objectos" para construir

Várias Máquinas executam várias tarefas em paralelo

#### Remember:

In FPGAs there isn't:

Do this, after this, then that..

Em linguagens de alto nível por vezes confundem-se

#