# Projecto e Controlo em Lógica Digital

www.lip.pt/~pedjor/PCLD

State Machines

#### **Refs:**

Cyclone II device Handbook, Altera corp.

Quartus II Handbook, Altera corp.

DE2 documentation

Verilog HDL, S. Palnitkar, Prentice Hall

# Sequential Logic

# ... Something we couldn't build with combinatorial logic

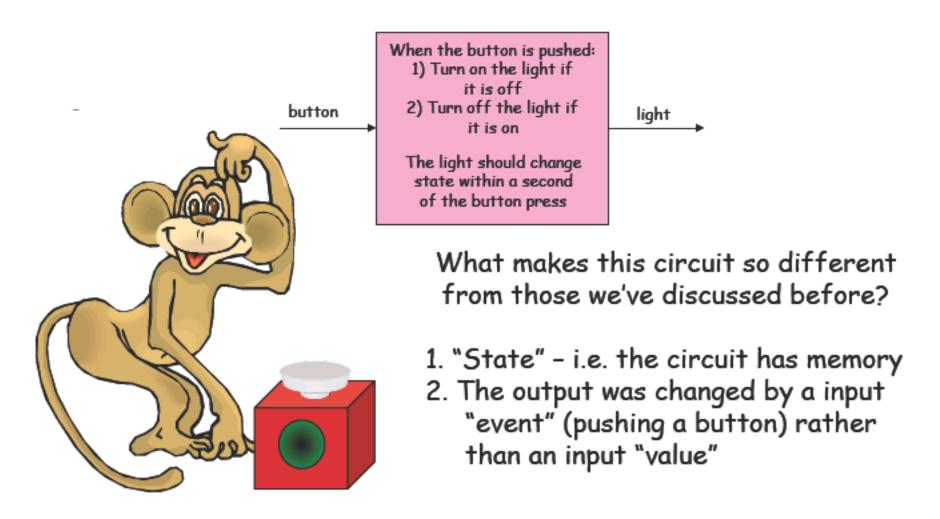

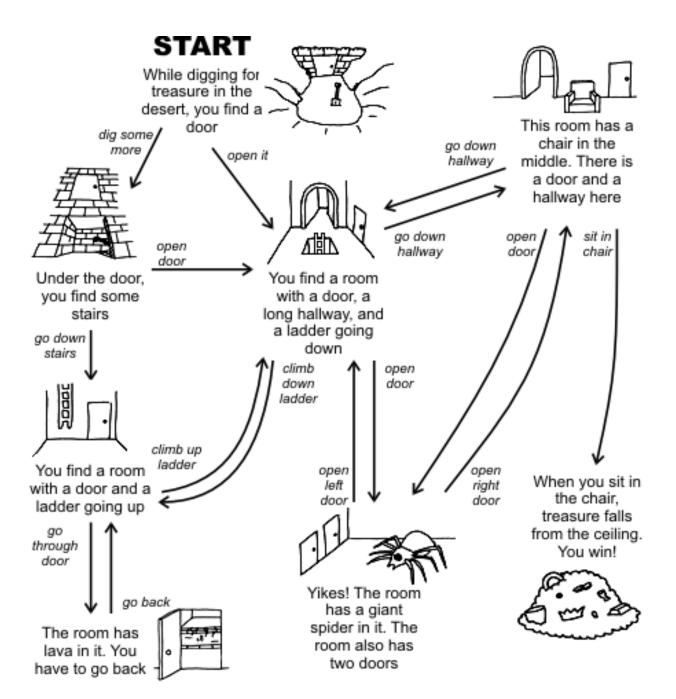

What if you were given the following design specification:

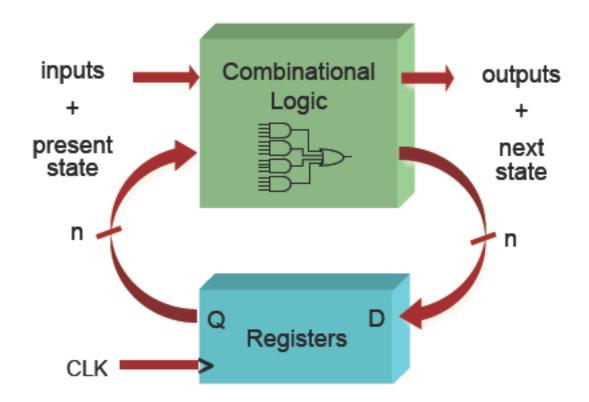

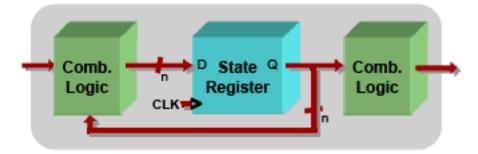

## Digital State

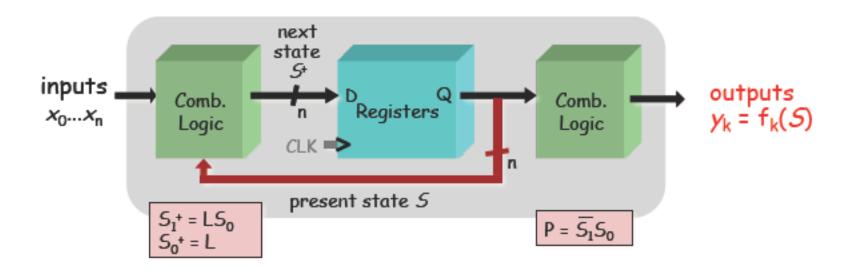

#### One model of what we'd like to build

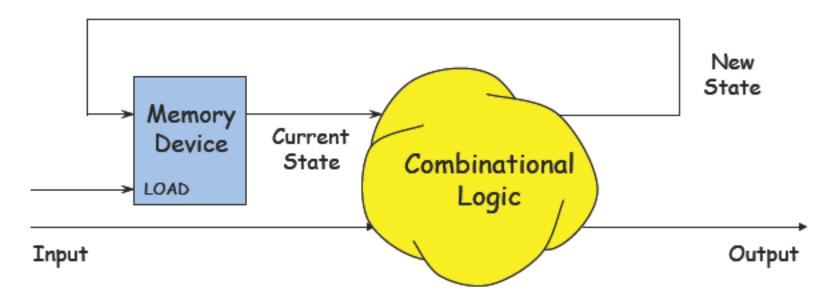

Plan: Build a Sequential Circuit with stored digital STATE -

- Memory stores CURRENT state, produced at output

- Combinational Logic computes

- NEXT state (from input, current state)

- OUTPUT bit (from input, current state)

- State changes on LOAD control input

when Output depends on input and current state, circuit is called a Mealy machine. If Output depends <u>only</u> on the current state, circuit is called a Moore machine.

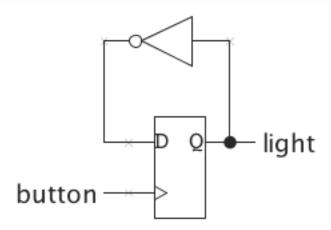

# Implementation for on/off button

module onoff(input button, output reg light);

always @(posedge button) light <= ~light;

endmodule</pre>

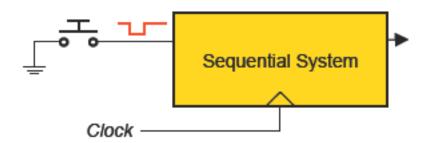

## Synchronous on/off button

When designing a system that accepts many inputs it would be hard to have input changes serve as the system clock (which input would we use?). So we'll use a single clock of some fixed frequency and have the inputs control what state changes happen on rising clock edges.

## Resetting to a known state

Usually one can't rely on registers powering-on to a particular initial state\*. So most designs have a RESET signal that when asserted initializes all the state to known, mutually consistent initial values.

<sup>\*</sup> Actually, our FPGAs will reset all registers to 0 when the device is programmed. But it's nice to be able to press a reset button to return to a known state rather than starting from scratch by reprogramming the device.

## Clocks are fast, we're slow!

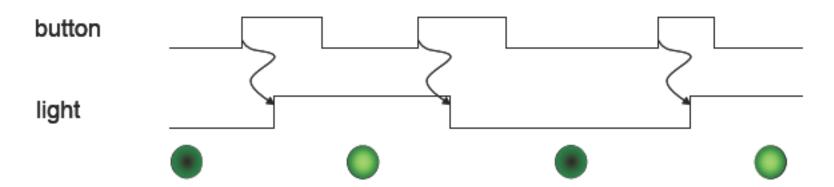

The circuit on the last slide toggles the light on every rising clock edge for which button is 1. But clocks are fast (27MHz!) and our fingers are slow, so how do we press the button for just one clock edge? Answer: we can't, but we can can add some state that remembers what button was last clock cycle and then detect the clock cycles when button changes from 0 to 1.

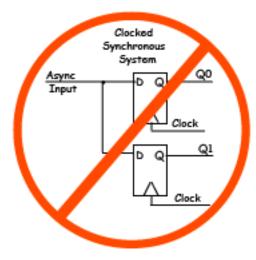

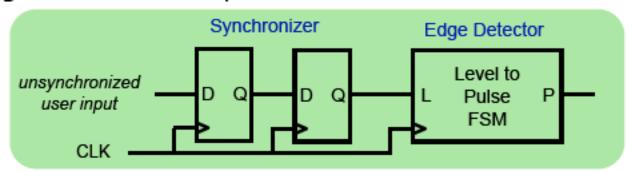

## Asynchronous Inputs in Sequential Systems

What about external signals?

Can't guarantee setup and hold times will be met!

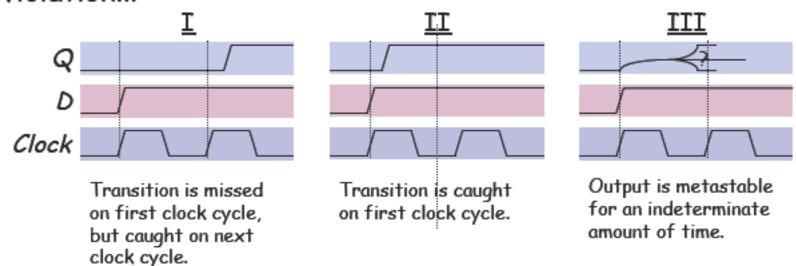

When an asynchronous signal causes a setup/hold violation...

Q: Which cases are problematic?

## Asynchronous Inputs in Sequential Systems

All of them can be, if more than one happens simultaneously within the same circuit.

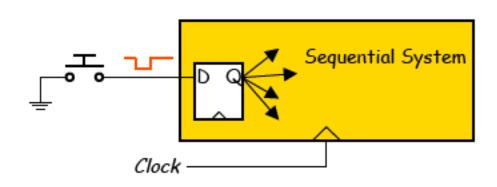

Guideline: ensure that external signals directly feed exactly one flip-flop

This prevents the possibility of I and II occurring in different places in the circuit, but what about metastability?

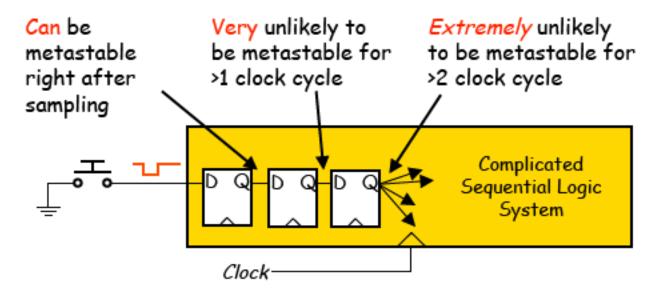

## Handling Metastability

- Preventing metastability turns out to be an impossible problem

- High gain of digital devices makes it likely that metastable conditions will resolve themselves quickly

- Solution to metastability: allow time for signals to stabilize

How many registers are necessary?

- Depends on many design parameters (clock speed, device speeds, ...)

- In 6.111, a pair of synchronization registers is sufficient

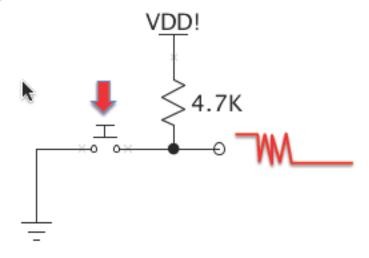

## One last little problem...

Mechanical buttons exhibit contact "bounce" when they change position, leading to multiple output transitions before finally stabilizing in the new position:

We need a debouncing circuit!

```

// Switch Debounce Module

// use your system clock for the clock input

// to produce a synchronous, debounced output

// DELAY = .01 sec with a 27Mhz clock

module debounce #(parameter DELAY=270000)

(input reset, clock, noisy,

output reg clean);

reg [18:0] count;

reg new;

always @(posedge clock)

if (reset) // return to known state

begin

count \leftarrow 0:

new <= noisy;

clean <= noisy;

end

else if (noisy != new) // input changed

begin

new <= noisy;

count \leftarrow 0;

end

else if (count == DELAY) // stable!

clean <= new;

else

// waiting...

count <= count+1;

endmodule.

```

## On/off button: final answer

```

module onoff_sync(input clk, reset, button_in,

output reg light);

// synchronizer

reg button, btemp;

always @(posedge clk)

{button,btemp} <= {btemp,button_in};

// debounce push button

wire bpressed;

debounce db1(.clock(clk),.reset(reset),

.noisy(button)..clean(bpressed));

req old_bpressed: // state last clk cycle

always @ (posedge clk) begin

if (reset)

begin light <= 0; old_bpressed <= 0; end</pre>

else if (old_bpressed==0 && bpressed==1)

// button changed from 0 to 1

light <= ~light;

old_bpressed <= bpressed;

end

endmodule

```

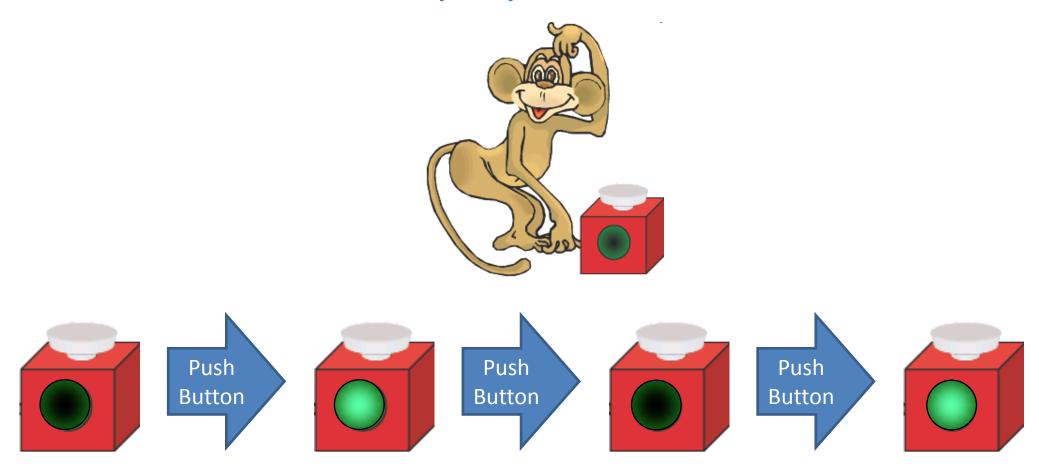

# A Simple problem...

al ways @ (posedge button)

begin

led<=~led;

end

## A Simple problem...

#### Question #1:

If the button has a value "low" the led should be 'ON" or "OFF"?

#### Question #2:

If the button has a value "high" the led should be 'ON" or "OFF"?

#### Question #3:

If the button is pressed the led should be 'ON" or "OFF"?

# Depends on the STATE!!

# This is a State machine!!

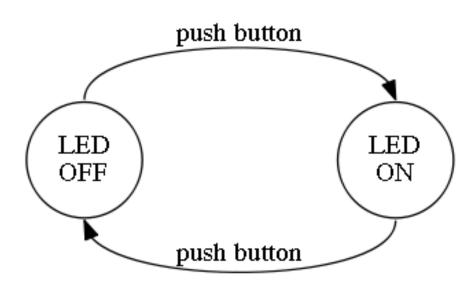

## A Simple problem...

Let's implement a state machine for this simple problem

State Diagram:

### **State Machines**

### Can get complicated...

## The worst one!!

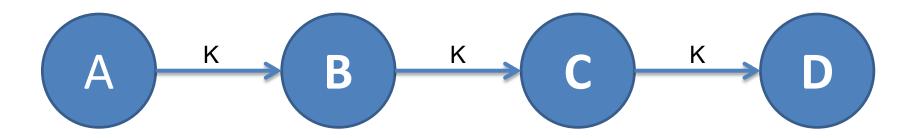

## Finite State Machines

- Finite State Machines (FSMs) are a useful abstraction for sequential circuits with centralized "states" of operation

- At each clock edge, combinational logic computes outputs and next state as a function of inputs and present state

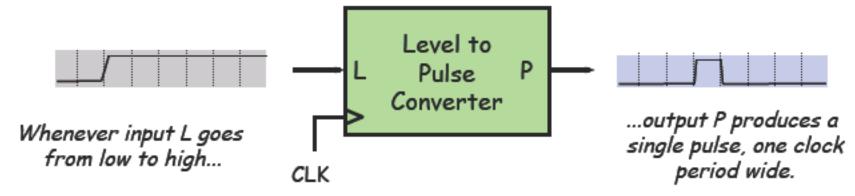

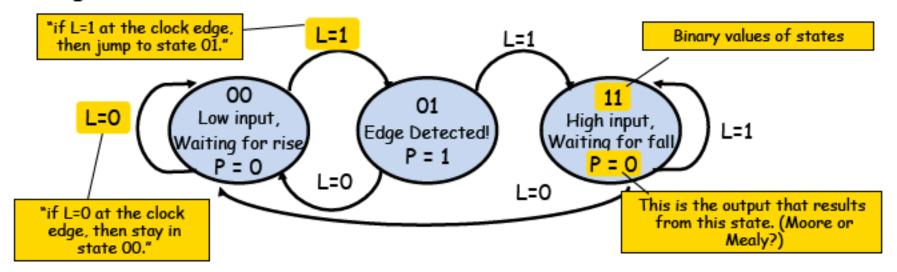

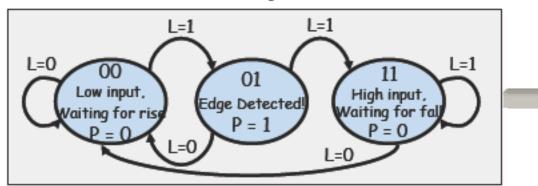

## Design Example: Level-to-Pulse

- A level-to-pulse converter produces a single -cycle pulse each time its input goes high.

- It's a synchronous rising-edge detector.

- Sample uses:

- Buttons and switches pressed by humans for arbitrary periods of time

- Single-cycle enable signals for counters

## Step 1: State Transition Diagram

Block diagram of desired system:

State transition diagram is a useful FSM representation and design aid:

In each state there should be one and only one arc for each input combination.

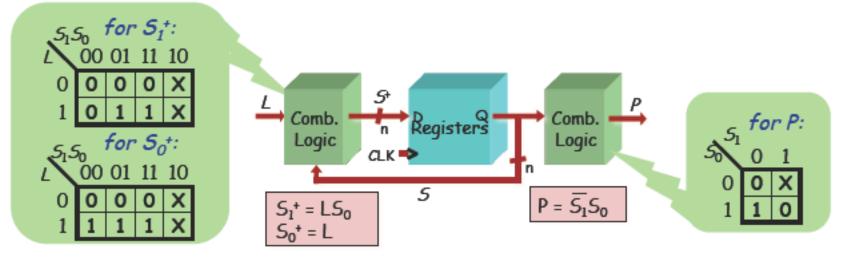

## Choosing State Representation

Choice #1: binary encoding

For N states, use ceil(log<sub>2</sub>N) bits to encode the state with each state represented by a unique combination of the bits. Tradeoffs: most efficient use of state registers, but requires more complicated combinational logic to detect when in a particular state.

Choice #2: "one-hot" encoding

For N states, use N bits to encode the state where the bit corresponding to the current state is 1, all the others 0. Tradeoffs: more state registers, but often much less combinational logic since state decoding is trivial.

## Step 2: Logic Derivation

Transition diagram is readily converted to a state transition table (just a truth table)

| Current<br>State |                       | In | Next<br>State |             | Out |

|------------------|-----------------------|----|---------------|-------------|-----|

| 5,               | <b>5</b> <sub>0</sub> | L  | <i>5₁</i> ⁺   | <b>5</b> ₀⁺ | P   |

| 0                | 0                     | 0  | 0             | 0           | 0   |

| 0                | 0                     | 1  | 0             | 1           | 0   |

| 0                | 1                     | 0  | 0             | 0           | 1   |

| 0                | 1                     | 1  | 1             | 1           | 1   |

| 1                | 1                     | 0  | 0             | 0           | 0   |

| 1                | 1                     | 1  | 1             | 1           | 0   |

Combinational logic may be derived using Karnaugh maps

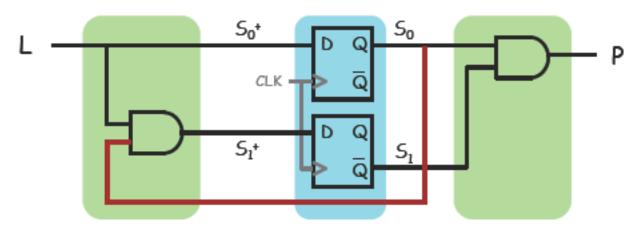

## Moore Level-to-Pulse Converter

### Moore FSM circuit implementation of level-to-pulse converter:

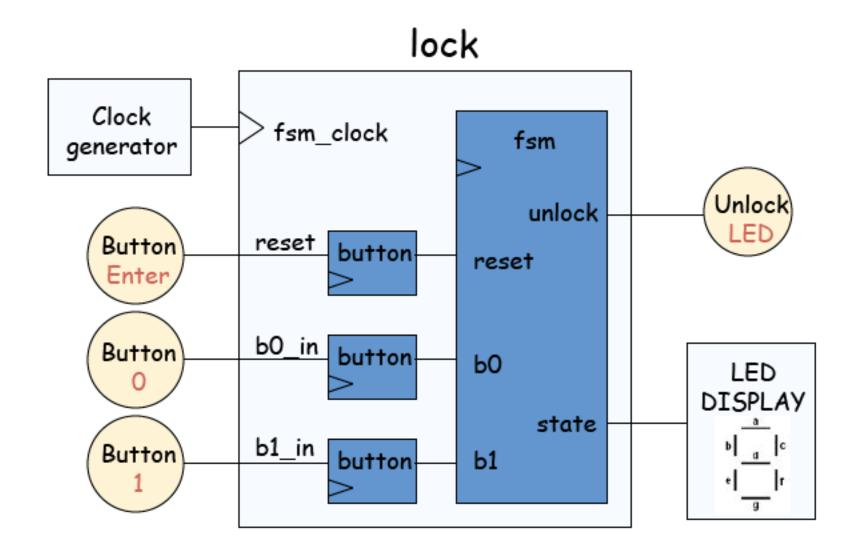

## FSM Example

#### GOAL:

Build an electronic combination lock with a reset button, two number buttons (0 and 1), and an unlock output. The combination should be 01011.

#### STEPS:

- Design lock FSM (block diagram, state transitions)

- Write Verilog module(s) for FSM

# Step 1A: Block Diagram

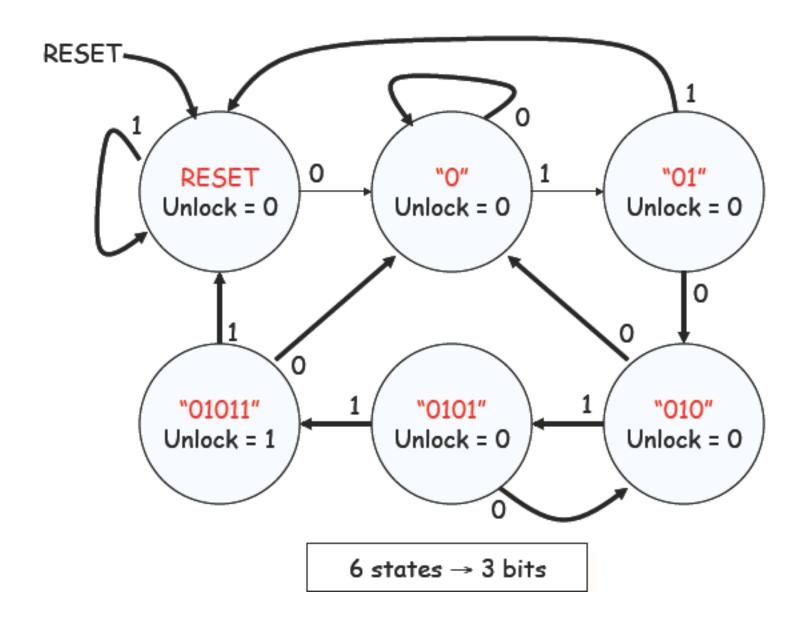

## Step 1B: State transition diagram

## Step 2: Write Verilog

```

// synchronize push buttons, convert to pulses

// implement state transition diagram

reg [2:0] state,next_state;

always @(*) begin

// combinational logic!

next_state = ???;

end

always @(posedge clk) state <= next_state;</pre>

// generate output

assign out = ???;

// debugging?

endmodule

```

## Step 2A: Synchronize buttons

```

// button

// push button synchronizer and level-to-pulse converter

// OUT goes high for one cycle of CLK whenever IN makes a

// low-to-high transition.

module button(

input clk, in,

output out

);

clk-

reg r1, r2, r3;

always @(posedge clk)

synchronizer

state

begin

r1 <= in; // first reg in synchronizer

r2 <= r1; // second reg in synchronizer, output is in sync!

r3 <= r2; // remembers previous state of button

end

// rising edge = old value is 0, new value is 1

assign out = \simr3 & r2;

endmodule

```

## Step 2B: state transition diagram

```

parameter S_RESET = 0; // state assignments

parameter S_0 = 1:

parameter S_01 = 2;

parameter S_010 = 3;

"01"

Unlock = 0

Unlock = 0

Unlock = 0

parameter S_0101 = 4;

parameter S_01011 = 5;

*01011 *

"0101"

reg [2:0] state, next_state;

Unlock = 1

Unlock = 0

Unlock = 0

always @(*) begin

// implement state transition diagram

if (reset) next_state = S_RESET;

else case (state)

S_RESET: next_state = b0 ? S_0 : (b1 ? S_RESET : state);

S_0: next_state = b0 ? S_0 : (b1 ? S_01 : state);

S_01: next_state = b0 ? S_010 : (b1 ? S_RESET : state);

S_010: next_state = b0 ? S_0 : (b1 ? S_0101 : state);

S_0101: next_state = b0 ? S_010 : (b1 ? S_01011 : state);

S_01011: next_state = b0 ? S_0 : (b1 ? S_RESET : state);

default: next_state = S_RESET; // handle unused states

endcase

end

always @(posedge clk) state <= next_state;

```

# Step 2C: generate output

```

// it's a Moore machine! Output only depends on current state

assign out = (state == S_01011);

```

## Step 2D: debugging?

```

// hmmm. What would be useful to know? Current state?

assign hex_display = {1'b0,state[2:0]};

```

Step 2: final Verilog implementation

```

module lock(input clk, reset in, b0 in, b1 in,

output out, output [3:0] hex display);

wire reset, b0, b1; // synchronize push buttons, convert to pulses

button b reset(clk, reset in, reset);

button b 0(clk,b0 in,b0);

button b 1(clk,bl in,bl);

parameter S RESET = 0; parameter S 0 = 1; // state assignments

parameter S 01 = 2; parameter S 010 = 3;

parameter S 0101 = 4; parameter S 01011 = 5;

reg [2:0] state, next state;

always @(*) begin

// implement state transition diagram

if (reset) next state = S RESET;

else case (state)

S_RESET: next_state = b0 ? S_0 : (b1 ? S_RESET : state);

S_0:    next_state = b0 ? S_0 : (b1 ? S_01 : state);

S_01:    next_state = b0 ? S_010 : (b1 ? S_RESET : state);

S 010: next state = b0 ? S 0 : (b1 ? S 0101 : state);

S 0101: next state = b0 ? S 010 : (b1 ? S 01011 : state);

S_01011: next_state = b0 ? S_0 : (b1 ? S_RESET : state);

default: next state = S RESET; // handle unused states

endcase

end

always @(posedge clk) state <= next state;

assign out = (state == S_01011);  // assign output: Moore machine

assign hex display = {1'b0,state}; // debugging

endmodule

```

## Partitioning state machines

Basically the trick is that you need to put the top one on hold

# Partitioning state machines

Basically the trick is that you need to put the top one on hold

## Toward FSM Modularity

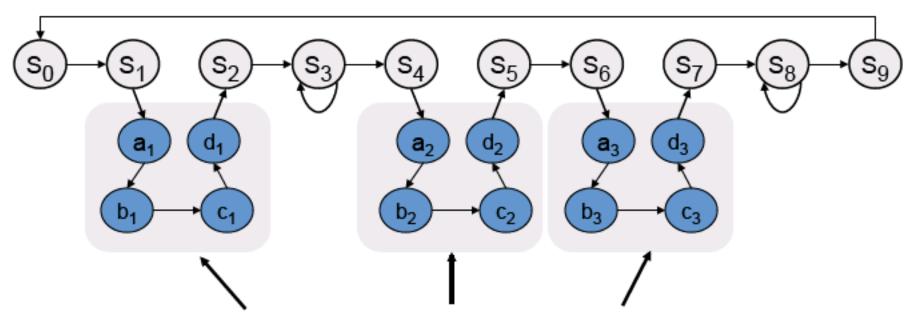

Consider the following abstract FSM:

- Suppose that each set of states a<sub>x</sub>...d<sub>x</sub> is a "sub-FSM" that produces exactly the same outputs.

- Can we simplify the FSM by removing equivalent states?

No! The outputs may be the same, but the next-state transitions are not.

- This situation closely resembles a procedure call or function call in software...how can we apply this concept to FSMs?

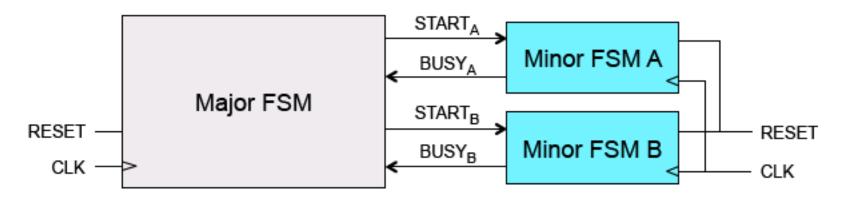

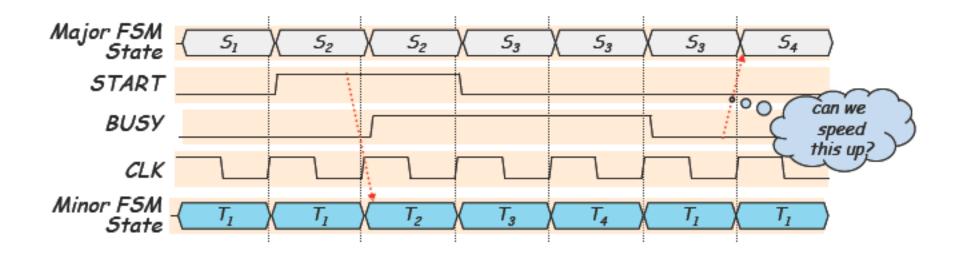

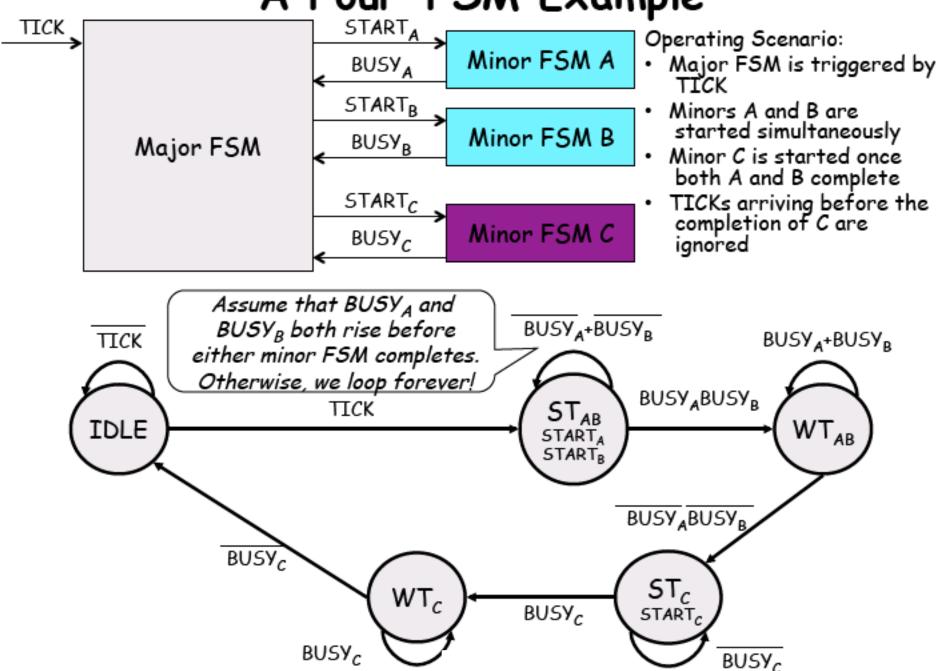

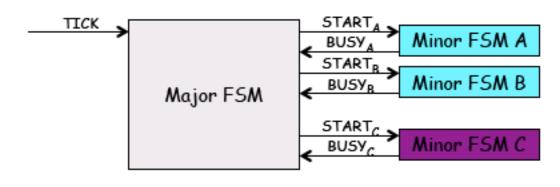

## The Major/Minor FSM Abstraction

- Subtasks are encapsulated in minor FSMs with common reset and clock

- Simple communication abstraction:

- START: tells the minor FSM to begin operation (the call)

- BUSY: tells the major FSM whether the minor is done (the return)

- The major/minor abstraction is great for...

- Modular designs (always a good thing)

- Tasks that occur often but in different contexts

- Tasks that require a variable/unknown period of time

- Event-driven systems

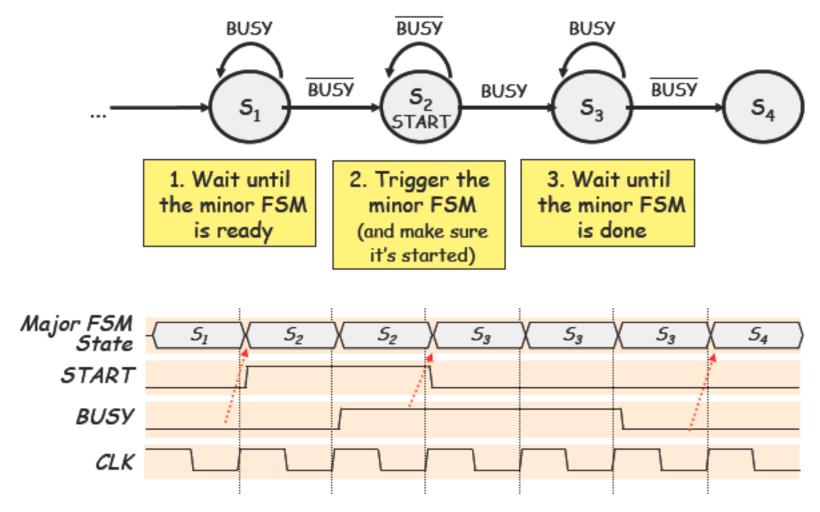

## Inside the Major FSM

#### Variations:

- Usually don't need both Step 1 and Step 3

- One cycle "done" signal instead of multi-cycle "busy"

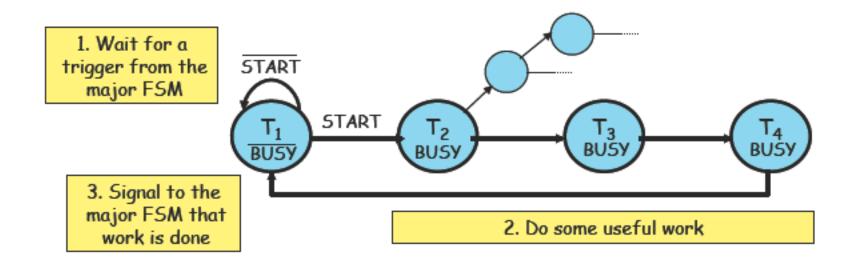

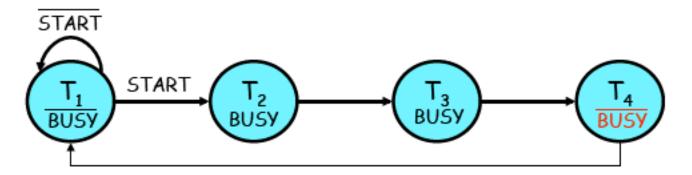

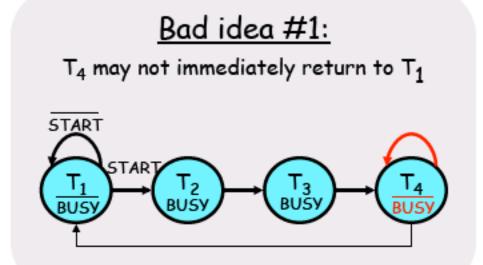

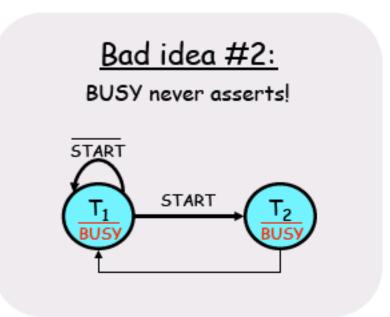

# Inside the Minor FSM

# Optimizing the Minor FSM

Good idea: de-assert BUSY one cycle early

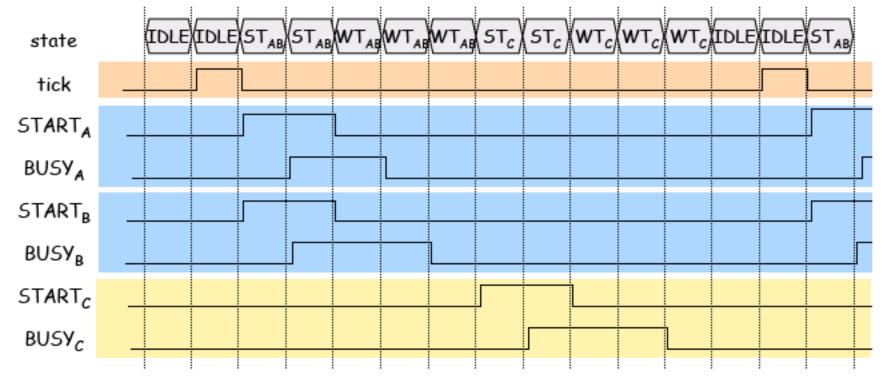

A Four-FSM Example

# Four-FSM Sample Waveform

# How to write a state machine in verilog

```

input k1, k2, k3, clk;

output 11, 12, 13;

//create registers

//to "store state"

reg [3:0] state, next;

//use parameters to give names

//to states

parameter s1=0;

parameter s2=1;

parameter s3=2;

parameter s4=3;

//The core code

//this, and only this,

//changes the states

al ways @ (posedge clk)

state<=next;

```

```

//decide which will be

//the next state

always @ (state or k1 or k2 or k3)

case (state)

S1:

if(????) next=????:

else next=S1:

S2:

if(????) next=????;

else next=S2: //The wait modes

S3:

if(????) next=????;

else next=S3;

//compute output

//according to state and/or input

assign l1= S1;

assi gn 12=S2 || S3;

assign 13=S3;

```

# A vending machine

- All selections are \$0.30.

- The machine makes change.

(Dimes and nickels only.)

- Inputs: limit 1 per clock

- □ Q quarter inserted

- □ D dime inserted

- □ N nickel inserted

- Outputs: limit 1 per clock

- □ DC dispense can

- □ DD dispense dime

- □ DN dispense nickel

# What states?

A starting (idle) state:

A state for each possible amount of money captured:

What's the maximum amount of money captured before purchase?

25 cents (just shy of a purchase) + one quarter (largest coin)

States to dispense change (one per coin dispensed):

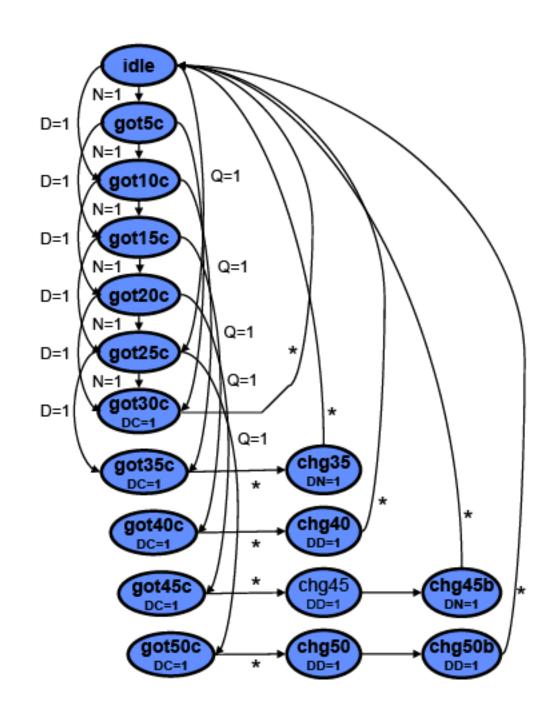

# A Moore vender

Here's a first cut at the state transition diagram.

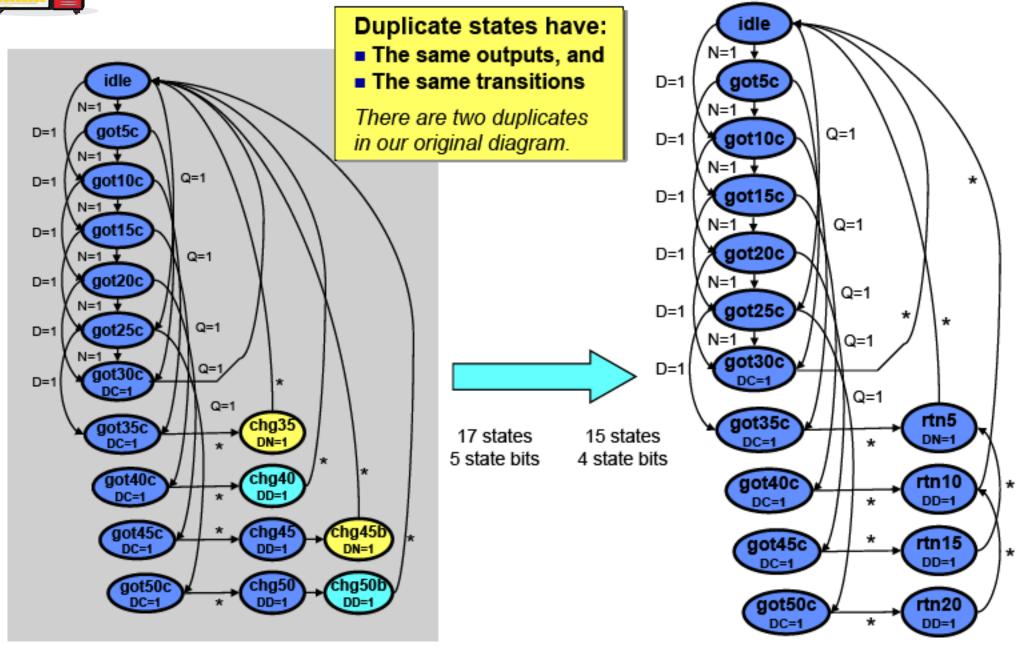

# State reduction

# The verilog code

# FSMs are easy in Verilog. Simply write one of each:

- State register (sequential always block)

- Next-state combinational logic (comb. always block with case)

- Output combinational logic block (comb. always block or assign statements)

```

module mooreVender (N, D, Q, DC, DN, DD,

clk, reset, state);

input N, D, Q, clk, reset;

output DC, DN, DD;

output [3:0] state;

reg [3:0] state, next;

```

### States defined with parameter keyword

```

parameter IDLE = 0;

parameter GOT_5C = 1;

parameter GOT_10C = 2;

parameter GOT_15C = 3;

parameter GOT_20C = 4;

parameter GOT_25C = 5;

parameter GOT_30C = 6;

parameter GOT_35C = 7;

parameter GOT_40C = 8;

parameter GOT_45C = 9;

parameter GOT_50C = 10;

parameter RETURN_15C = 12;

parameter RETURN_15C = 12;

parameter RETURN_5C = 14;

```

# State register defined with sequential always block

```

always @ (posedge clk or negedge reset)

if (!reset) state <= IDLE;

else state <= next;</pre>

```

# The Verilog code

## Next-state logic within a combinational always block

```

always @ (state or N or D or Q) begin

case (state)

IDLE:

if (Q) next = GOT 25c;

else if (D) next = GOT 10c;

else if (N) next = GOT_5c;

else next = IDLE;

GOT 5c:

if (Q) next = GOT 30c;

else if (D) next = GOT 15c;

else if (N) next = GOT 10c;

else next = GOT_5c;

GOT 10c: if (Q) next = GOT 35c;

else if (D) next = GOT 20c;

else if (N) next = GOT 15c;

else next = GOT 10c;

GOT 15c: if (Q) next = GOT 40c;

else if (D) next = GOT_25c;

else if (N) next = GOT 20c;

else next = GOT_15c;

GOT 20c: if (Q) next = GOT 45c;

else if (D) next = GOT 30c;

else if (N) next = GOT 25c;

else next = GOT_20c;

```

```

GOT_25c:

if (Q) next = GOT 50c;

else if (D) next = GOT 35c;

else if (N) next = GOT 30c;

else next = GOT 25c;

GOT 30c: next = IDLE;

GOT 35c: next = RETURN 5c;

GOT 40c: next = RETURN 10c;

GOT 45c: next = RETURN 15c;

GOT 50c: next = RETURN 20c;

RETURN 20c: next = RETURN 10c;

RETURN 15c: next = RETURN 5c;

RETURN 10c: next = IDLE;

RETURN 5c:

next = IDLE;

default: next = IDLE;

endcase

end

```

### Combinational output assignment

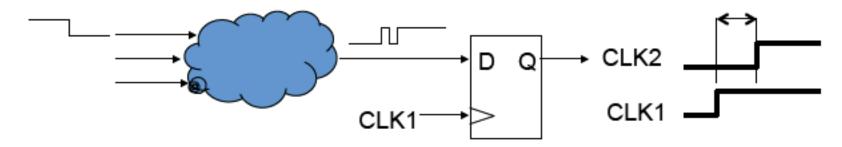

# Where should CLK come from?

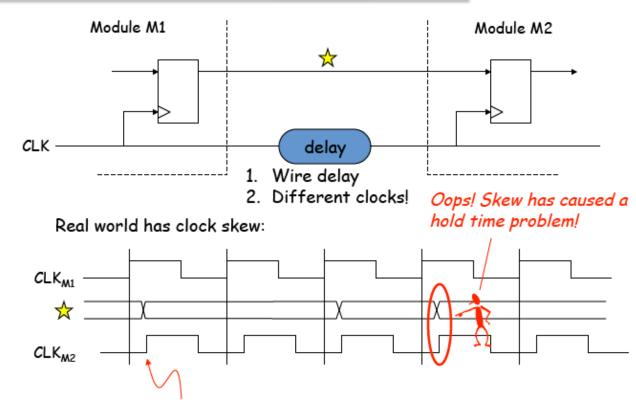

- Option 1: external crystal

- Stable, known frequency, typically 50% duty cycle

- Option 2: internal signals

- Option 2A: output of combinational logic

- No! If inputs to logic change, output may make several transitions before settling to final value → several rising edges, not just one! Hard to design away output glitches...

- Option 2B: output of a register

- Okay, but timing of CLK2 won't line up with CLK1

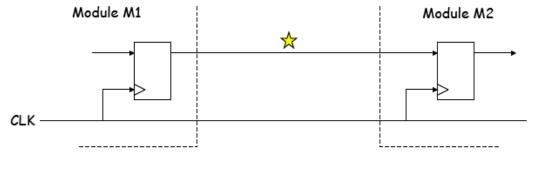

Clocking in and ideal world

### Ideal world:

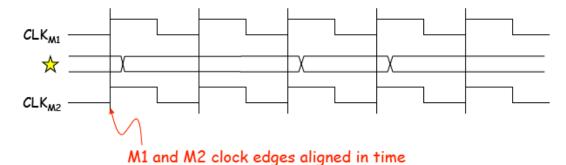

Clocking in a not so perfect reality

FPGAs contain global clock lines that have low skew. Number is limited

M2 clock delayed with respect to M1 clock

# Clocks with periods multiple of two

```

reg clk2,clk4,clk8,clk16;

always @(posedge clk) clk2 <= ~clk2;

always @(posedge clk2) clk4 <= ~clk4;

always @(posedge clk4) clk8 <= ~clk16;

always @(posedge clk8) clk16 <= ~clk16;</pre>

```

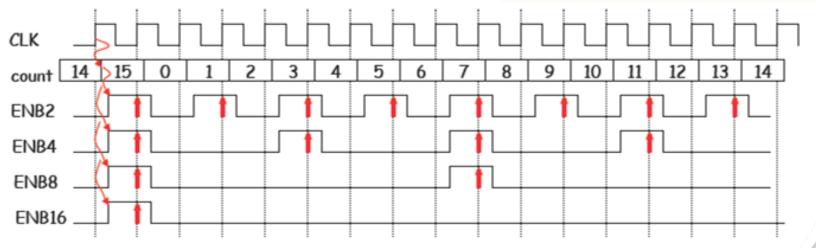

# Solution: 1 clock, many enables

Use one (high speed) clock, but create enable signals to select a subset of the edges to use for a particular piece of sequential logic

```

reg [3:0] count;

always @(posedge clk) count <= count + 1;  // counts 0..15

wire enb2 = (count[0] == 1'b1);

wire enb4 = (count[1:0] == 2'b11);

wire enb8 = (count[2:0] == 3'b111);

wire enb16 = (count[3:0] == 4'b1111);

// get here every 2<sup>nd</sup> cycle end

```

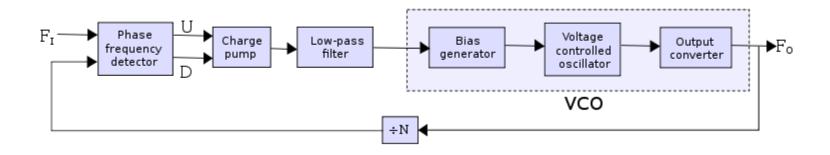

# The Phase Locked Loop (PLL)

A feature available in Cyclone II devices that employs a phase-locked loop (PLL). The Cyclone II PLL provides advanced multiplication, programmable duty cycle, phase shifting, programmable bandwidth, manual clock switchover, clock outputs driving all networks, and a source synchronous mode.

You can take advantage of the Cyclone II PLL with the altpll megafunction.

# **Phase-Locked Loops (ALTPLL)**

# **Megafunction User Guide**

#

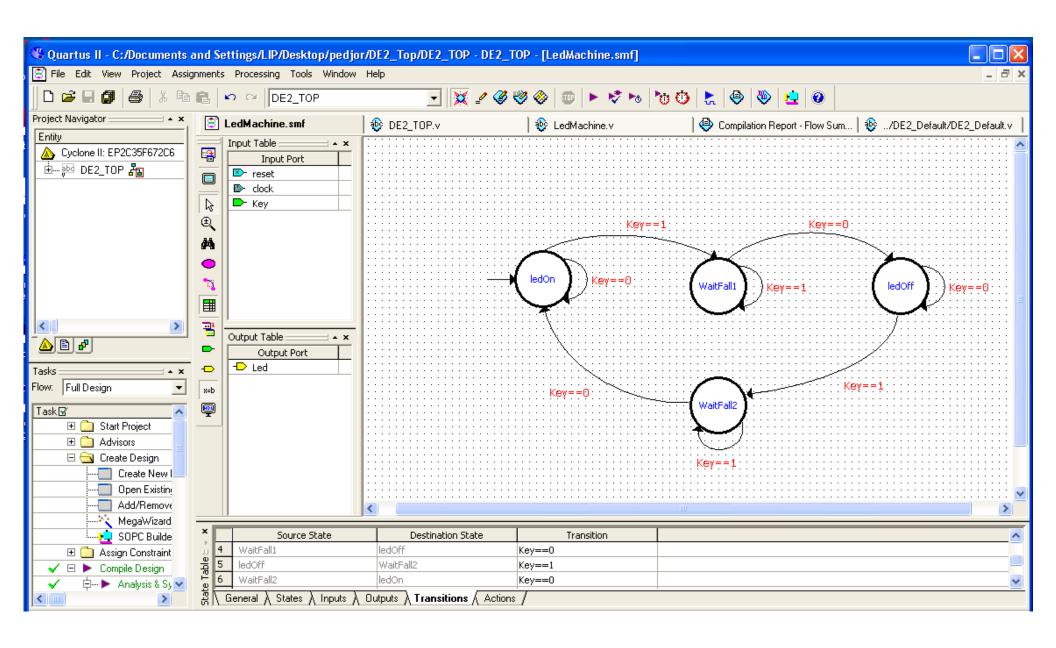

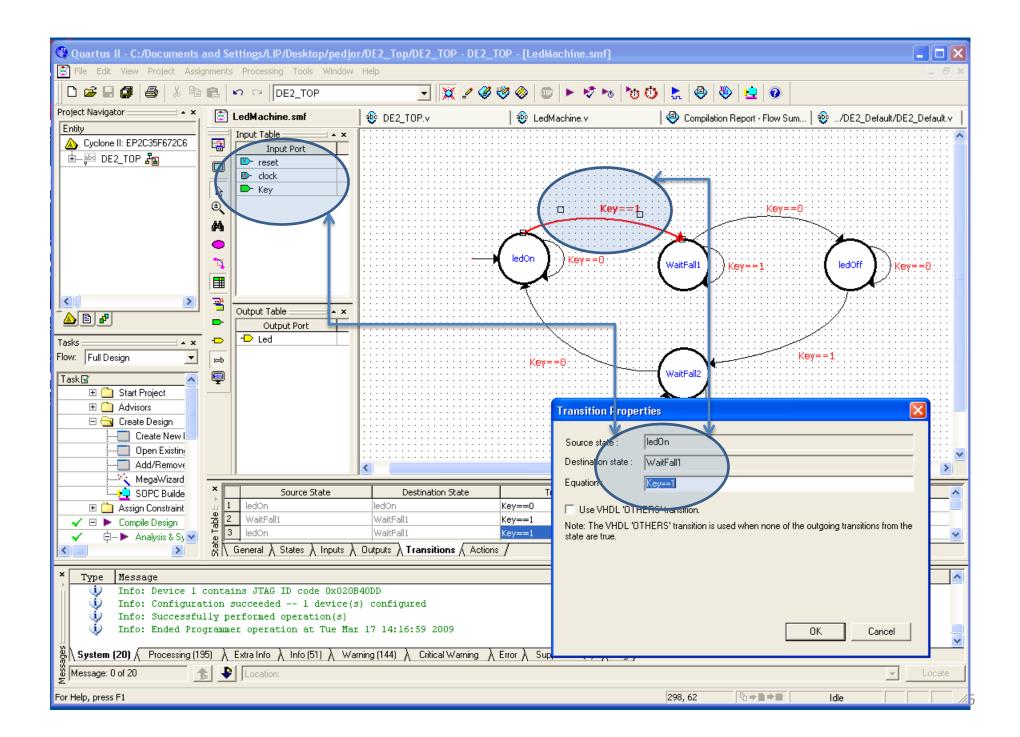

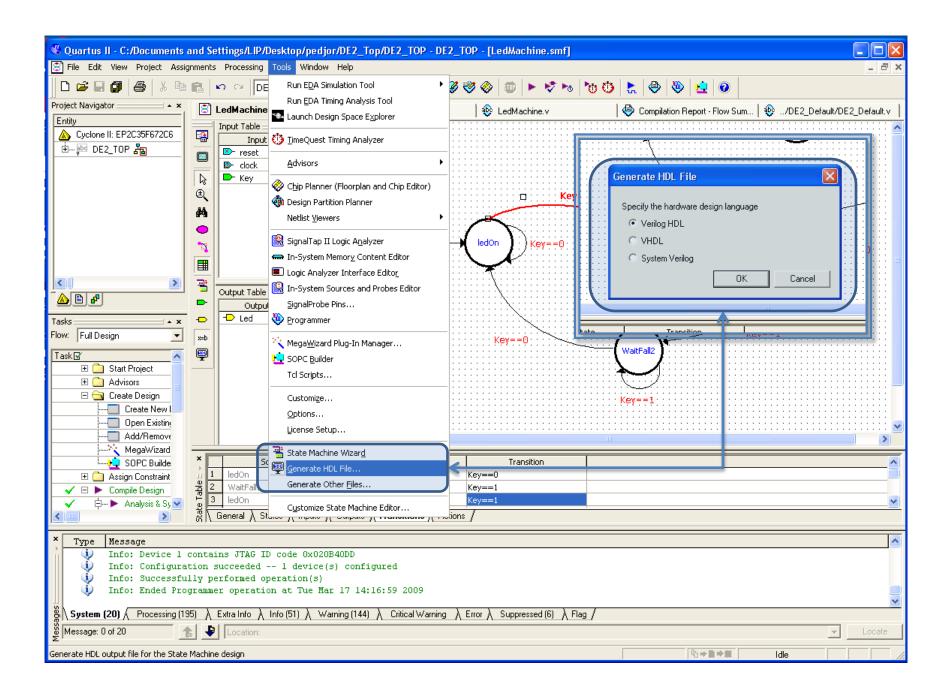

# File > new > statemachine

For more information about creating and editing state machine diagrams, refer to the Quartus II Help.

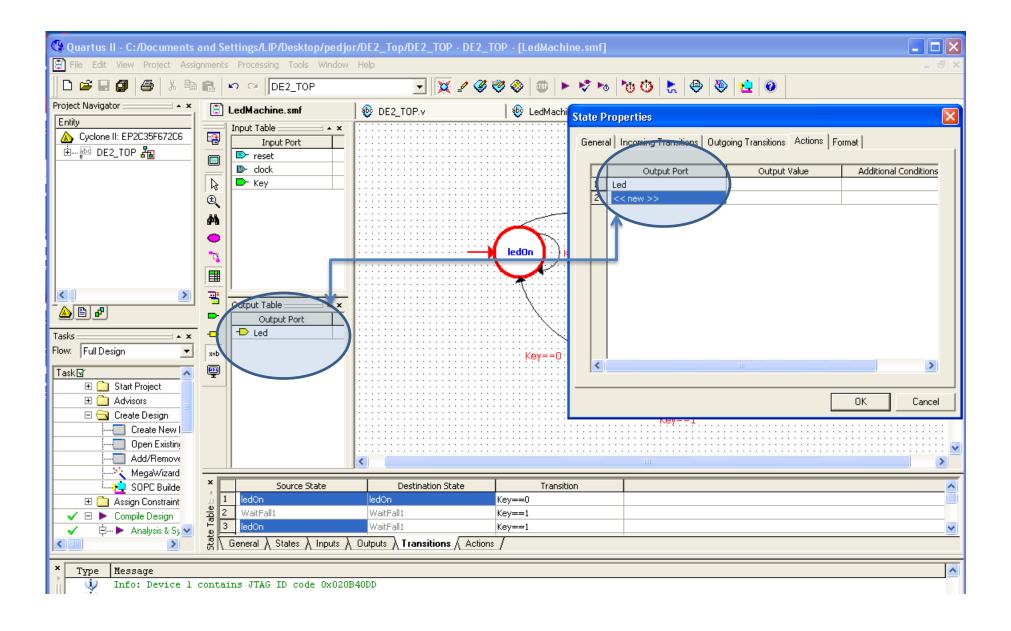

# Define the states output

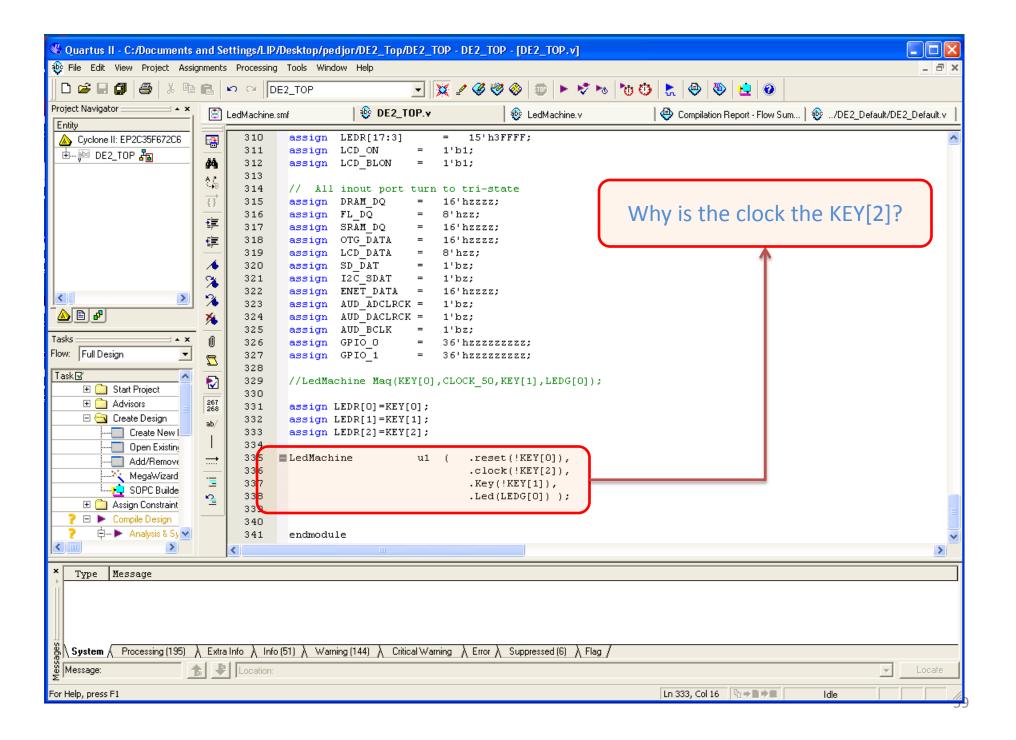

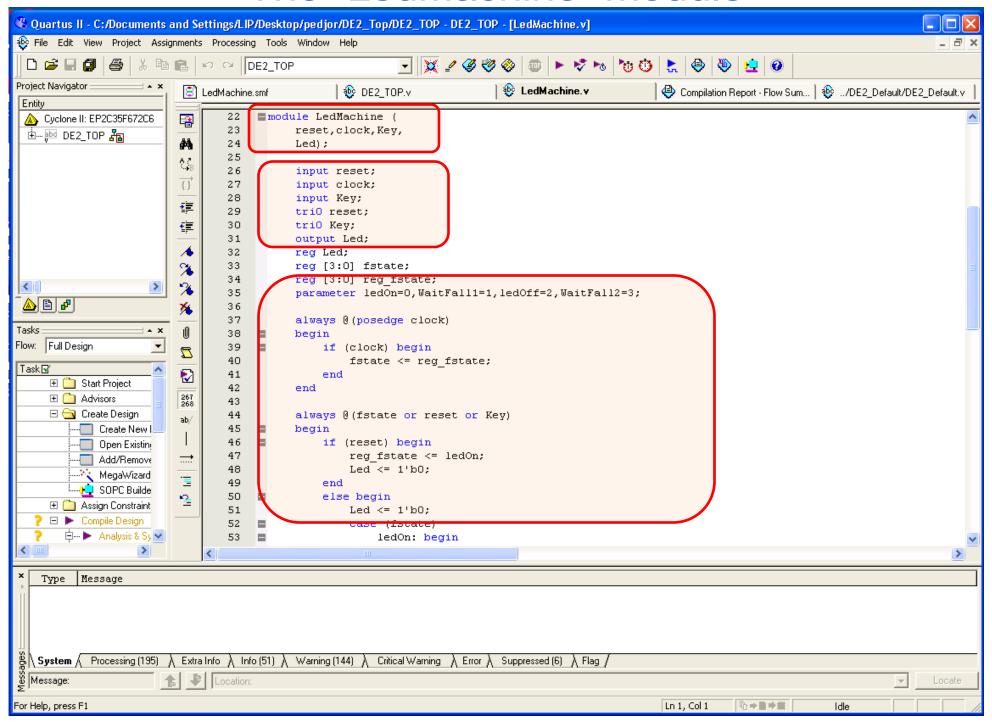

# The "LedMachine" module

# The top design