## 3º Laboratório

### Trabalho 1

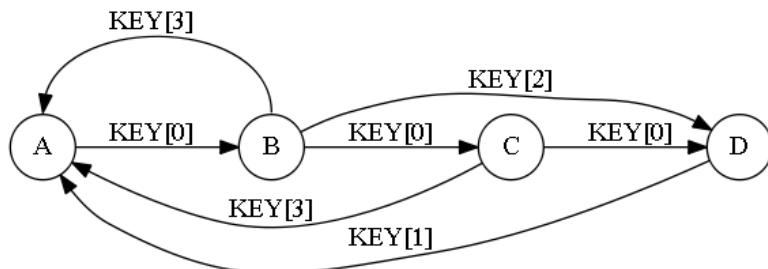

Implemente a máquina de estados representada pelo seguinte diagrama. Use uma construção “standard” da linguagem Verilog.

Quando a máquina estiver no estado “D” todos os leds verdes devem estar acensos. Nos outros estados os leds verdes devem estar desligados.

Utilize os leds vermelhos para indicar o estado actual da máquina.

### Trabalho 2

Implementar uma máquina de estados para o controle de um osciloscópio.

Um osciloscópio digital tem, tipicamente, vários subsistemas que realizam diferentes tarefas. Entre os mais importantes conta-se o sistema de conversão analógico-digital que origina um fluxo “continuo” de dados, o sistema de trigger que analisa “online” o fluxo de dados para seleccionar zonas com interesse, um sistema de memória temporária para “buffering” e um sistema de controlo, responsável pela gestão global do sistema, normalmente realizado com uma máquina de estados. Pretende-se implementar uma máquina de estados para o controlo de um osciloscópio.

#### Descrição da funcionalidade.

O osciloscópio inicia num estado “idle”. Após receber um comando “arm” dado por “KEY[0]” o osciloscópio entra num mode de pre-trigger em que sinaliza ao subsistema de memória para encher uma memória de buffer. Após encher a esta memória o osciloscópio fica à espera de um sinal do subsistema de trigger eliminando o valor mais antigo e gravando um novo valor. Após o sinal de trigger é dada ordem ao subsistema de memória para acabar de encher a memória. Em seguida o osciloscópio deve ficar em espera até ser lido após o que deve voltar para o estado “idle”

Preveja um reset global que traz o osciloscópio para o estado “idle”

Não estando disponíveis os outros subsistemas, utilize interruptores, botões de pressão, etc. para simular as linhas de controlo, nomeadamente o estado das memórias

Desenhe o diagrama de estados e em seguida implemente em verilog usando uma construção “standard”